# FIRMWARE for FADC250 Ver2 ADC FPGA

#### **Table of Content:**

- 1. Functional (Requirement) Description

- a. Overview

- b. Pedestal Subtraction

- c. Programmable Pulse Generator.

- d. Channel Data Processing

- i. Option 1: Raw Mode

- ii. Option 2: Pulse Mode

- iii. Option 3: Integral

- iv. Trigger Input Buffer

- e. Triggering Options

- f. Energy Sum

- g. Acceptance Pulse (Hit Bits)

- 2. Conceptual Architecture Diagram.

- a. Overview

- b. Data Buffer

- c. Process Algorithm

- d. VME FPGA Interface

- 3. Data Format

- a. Internal

- b. To FIFO (to VME FPGA)

- c. To Hit Sum FPGA

- 4. Modified Fast Bus Address Mapping

- 5. VHDL Block Diagram

- 6. VHDL Test Bench and Test Vector.

- 7. Size, Power, and Performance

**ADC FPGA Functional Description**

### **Overview:**

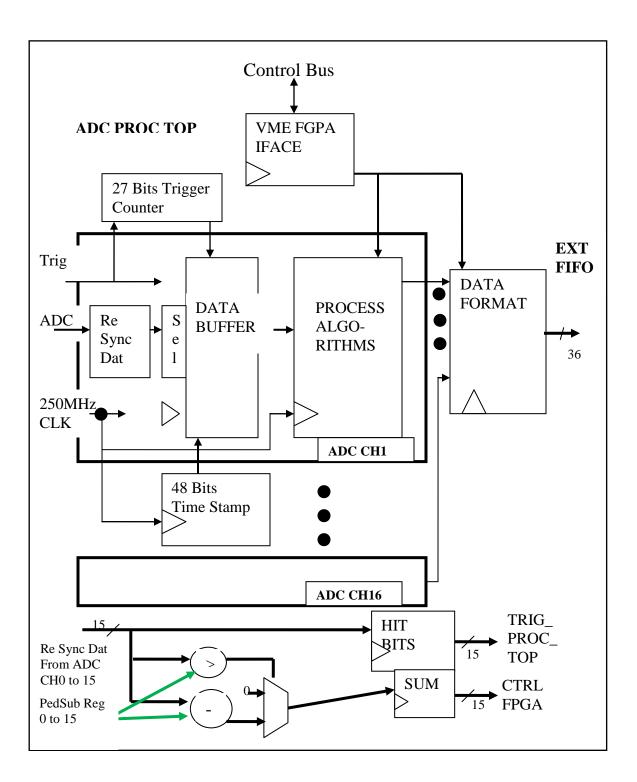

The ADC FPGA receives 12-bit data words streaming at 250 MHz from 16 ADC. It performs **Channel Data Processing** for each ADC, computes **Energy Sum** of all ADC, and generates **Acceptance Pulse** for each ADC. The data selected in Channel Data Processing and results of Energy Sum are passed to CTRL FPGA to be sent to VME host and CTP respectively. The code is modular such that processing algorithms can easily be added or deleted.

#### **Pedestal Subtraction:**

Samples received from the ADC are immediately subtracted from a programmable pedestal value before any further processing. The result is not allowed to go below zero. Each of the ADC has a separate pedestal value.

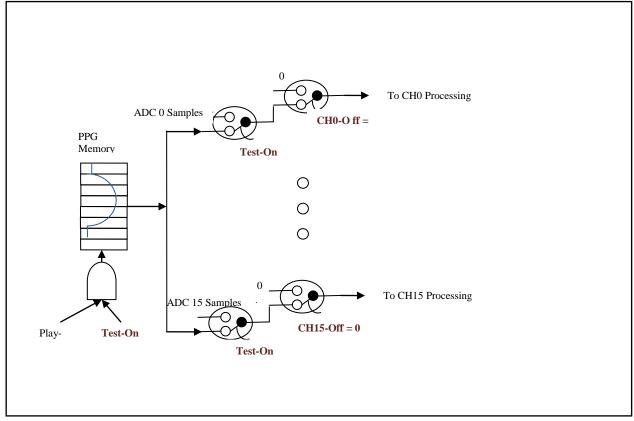

#### **Programmable Pulse Generator (PPG):**

Input to Channel Data Processing can either come from ADC after pedestal subtraction or the Programmable Pulse Generator (PPG). Users can load simulated PMT data into the PPG via VME host. When a trigger occurs in test mode, the stored data is read and apply to Channel Data Processing. There are 16 PPG, one for each ADC channel and each PPG can hold 32 samples.

## 1. Channel Data Processing:

ADC Data

Trigger Input

Time Line

|←Programmable Trigger Window→| ------ 100nS to 2uS ------

|←-----Programmable Latency (100nS to 8uS ------→ |

Data from ADC are stored continuously in circular buffer until Trigger input becomes active (low). The data that was stored from the time that the Trigger occurs back to the time specified by Programmable Latency within the Programmable Trigger Window are processed.

There are three main options to which these data are processed. The options are selectable by the user via VME register setting and two Trigger Inputs.

While data are being processed, ADC FPGA will continue storing incoming ADC data with no loss of data. Programmable Trigger Window (PTW) and Programmable Latency(PL) are common to all 8 ADC channels.

# **Option 1 (Raw Mode):**

Data within the Programmable Trigger Window [PTW] is passed with no further processing to the VME Host.

## **Option 1 Raw Mode Data to VME Host Illustration:**

## Trigger Input

### Time Line

|←Programmable Trigger Window→|

$\left| \leftarrow \text{------Programmable Latency} \right|$

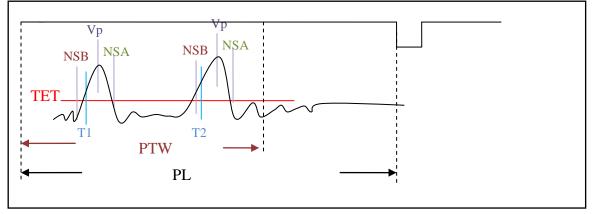

## **Option 2 (Pulse Mode) :**

When an ADC sample has a value that is greater than Programmable Trigger Energy Threshold (TET), the number of samples before (NSB) the Maximum value (Vp) and the number of samples after (NSA) Vp are sent to VME Host. NSB and NSA are programmable. T1 and T2 are described in TDC Algorithm. TET is 12 bits and unique to each ADC channel. NSB has a maximum value of 1024 NSA has a maximum value of 1024

#### **Option 2 Pulse Mode Data to VME Host Illustration:**

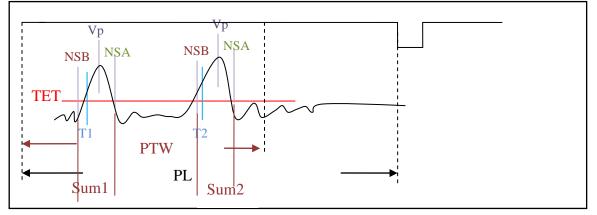

## **Option 3 Integral Mode:**

Data within NSB and NSA of Option 2 Raw Mode are summed around T1 and T2. PNS defines the number of samples before and after T1 and T2 include in Sum 1 and Sum 2 respectively. Only Sum 1, T1, Sum 2, and T2 are passed to VME FPGA. T1 and T2 are described in TDC Algorithm.

**Option 3 Integral ModevData to VME Host Illustration:**

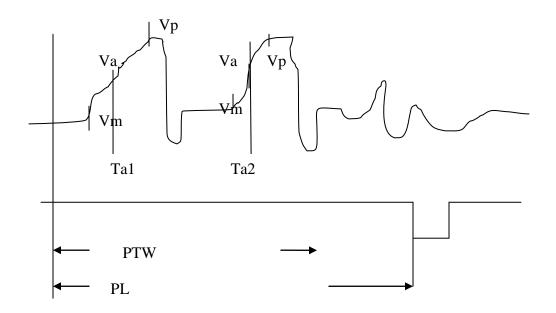

#### **TDC Algorithm:**

The TDC algorithm calculates time of the mid value (Va) of a pulse relative to the beginning of the look back window. Va is the value between the smallest and the peak value (Vp) of the pulse. The smallest value (Vm) is the beginning of the pulse. The time consists of coarse time and fine time. The coarse time is the number of clock the sample value before the mid value and the fine time is the interpolating value of mid value away from next sample. The coarse value is 10 bits and the fine value is 6 bit. The resolution of LSB is 1/(CLK \* 64). For a 250MHz the resolution is 62.5 pS. For example for a 20MHz clock, a pulse time (Ta) value of 110 means the mid-point of the pulse occurred at 6.875nS (62.5pS \* 110) from the beginning of look back window.

#### **Requirements for TDC Algorithm:**

i) There must be at least 5 samples (background) before pulse. Four of these samples are used to determine the pedestal (Vnoise) floor. The minimum value of the pulse is the first value that is greater than Vnoise.

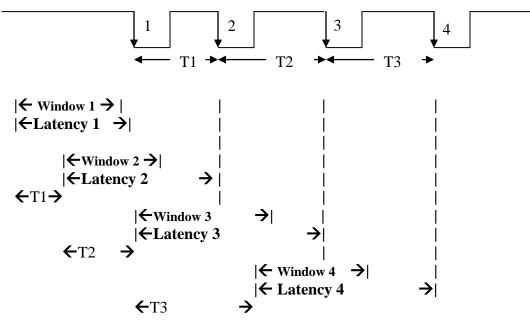

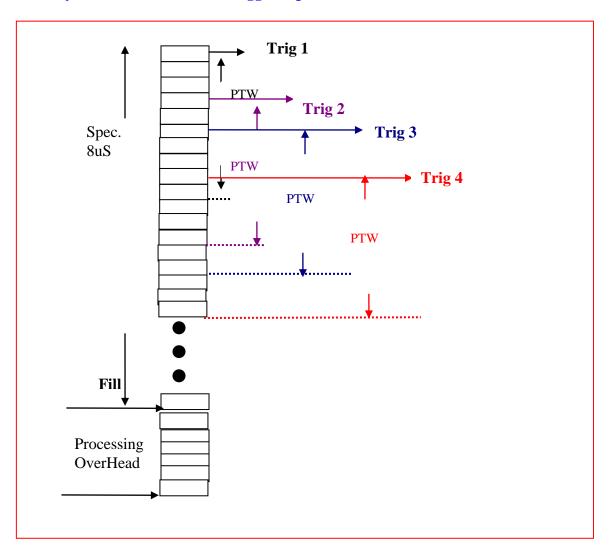

## **Trigger Input Buffer:**

In the event that the Trigger Input rate is faster than the data processing time, the processing algorithm has to be able to process 100 consecutives triggers with no loss in time lines. If a trigger cannot be processed due to an overflow condition, the VME FPGA will be notified: "no data for trigger. If T1, T2, or T3 is less than 50 Ns, the trigger will not be recorded.

#### **Successive Trigger Input Illustration:**

## **Trigger Options:**

The type of processing mode is determined by two trigger inputs and the two bits of a VME register setting. The Trigger Processing Mode table below shows the possible processing mode.

| Ingger Proce |               | 1                |

|--------------|---------------|------------------|

| VME Bits     | Trigger       | Modes            |

|              | Inputs        |                  |

|              | Trig2   Trig1 |                  |

| 00           | 00            | Idle             |

|              | 01            | Raw, Integral    |

|              | 10            | Integral         |

|              | 11            | Scaler Read Back |

| 01           | 00            | Idle             |

|              | 01            | Pulse, Integral  |

|              | 10            | Integral         |

|              | 11            | Scaler Read Back |

| 10           | XX            | Idle             |

| 11           | XX            | Idle             |

|              |               |                  |

Trigger Processing Mode:

# Memory Model for Successive Trigger Input Illustration:

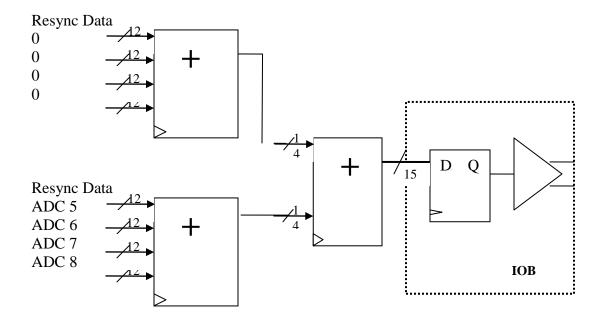

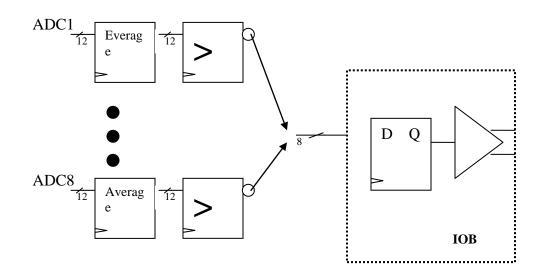

# 2. Energy Sum:

Data from ADC are added and the 16 bits-sum is sent to CTRL FPGA. Three stages pipeline adders are implemented to allow 250 MHz clocking. Sum valid signal accompanied the Sum.

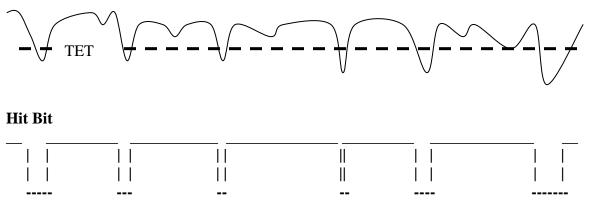

## 3. HITBITS:

When counts from an ADC channel are greater than threshold, the corresponding Hit Bit for that channel is high. The HitBits are processed by TRIG\_PROC\_TOP to form coincident trigger.

## **HitBits Illustration:**

#### ADC data

**Conceptual Architecture Diagram**

# **Overview:**

Data from each ADC is resynchronized with FPGA main CLK. The outputs of the Resync are inputs of Data Buffer, Pedestal Substraction, and Hit Bits circuits. Each ADC Channel has Resync, Data Buffer and Processing Circuits. The Data Buffer stores Resync Data, Trigger Number, and Time Stamp. Processing Circuit processes data from Data Buffer. Format read results from each ADC channels (0-15) Processing Circuit and mux it to external FIFO. For each of the ADC, Pedestal Subtraction Circuit subtracts a programmable constant from ADC sample if the sample is greater than the constant. If the sample is smaller than the constant, zero is output. The output of the Pedestal Subtraction Circuit is fed to the Sum circuit. Sum circuit adds the pedestal-subtracted-samples from each Pedestal Subtraction Circuit on a clock by clock basis. Bit Bits circuit compare Resync data to TET and produce a low active signal when Resync data is above TET.

The architecture supports Processing Modularity. Processing algorithms are independent of the other functions.

Sel block was added on March 3, 2008 to accommodate both 10 bits and 12 bits FADC boards This feature also allows individual ADC Channel values (counts) to be set to zero (effectively disable the ADC). CONF register (see below) configures these options.

On March 15, Sel block is expanded to include Programmable Pulse Generator.

#### Programmable Pulse Generator (PPG):

The PPG generates pulses by reading out digitized values of pulses (samples) stored in a memory. The memory has 32 locations. Each location has 16 bits and can hold one sample. Thirteen of the bits simulated the 12 data and 1 overflow bits output of the ADC implemented on the FAD250 board. The  $16^{th}$  bit facilitates writing and reading the memory. Samples are written to the PPG memory when VME write to address (0x0211 and 0x0011) and bit  $16^{th}$  is a one. The address automatically incremented after a sample is written. The last two samples written are required to have bit 16 zeroed (Sample value = 0x0000). After the last samples (0x0000) the address reset to the location of the first sample. Bits 14 and 15 are don't care bits. VME can verify the data is written by immediately read back the data (write follow by read).

Data are read out of PPG memory when Play-Back and Test-On are both logical one. The first location that will be read out is set by a register (Read-Out-Start-Address). Subsequent locations are read out at 4nS interval until Play-Back returns to logical zero. The read back cycles to Read-Out-Start-Address when bit 16<sup>th</sup> is a zero.

AUX\_IO(1) is used as Play-Back. Bit 7 of CONFIG register is used as Test-On Bit 8-15 of CONFIG register is used as CHx-OFF

For the FADC250 Version 1 the PPG can only hold 16 samples. The last two samples have to be written with 0x8000.

Test On is bit 6 of Configuration register. CHx-Off are bits 8-15 of configuration register.

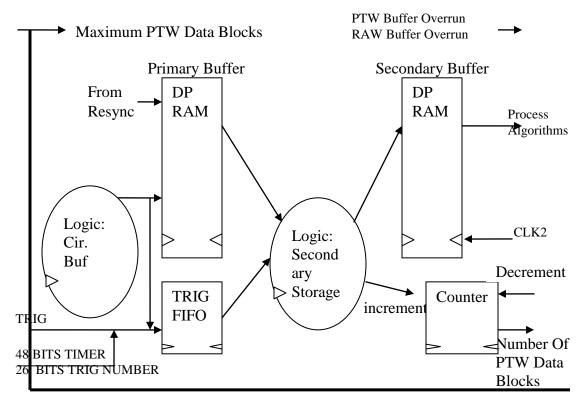

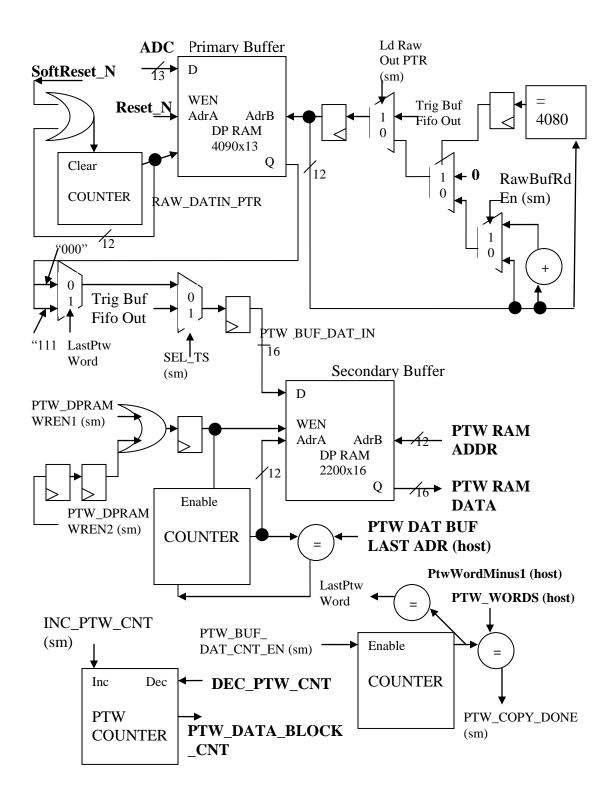

## **Data Buffer:**

- 1. Synchronize data from ADC to 250 MHz FPGA CLK

- 2. Store ADC data to Primary Buffer. Implement Primary Buffer as ring (circular) buffer.

- 3. When a Trigger occurs, the trigger is stored along with the values of the 48 Bits Timer and the Pointer of the Primary Buffer in a FIFO.

- 4. For each trigger, data within Programmable Trigger Window are copied from Primary Buffer to Secondary Buffer with time stamps and markers necessary for further processing. After the block is copied, Number of PTW Data Blocks increments by one.

- 5. After a block is read and process, Decrement should be pulsed to decrease th Number of PTW Data Blocks by one.

- 6. Each ADC channel has its own Data Buffer.

- 7. When the Trigger Rate is faster then the time needed to copy ADC Data from Primary Buffer to Secondary Buffer, RAW BUFFER OVERRUN is set and remain set until RESET\_N or SOFT\_RESET\_N goes low.

- 8. When Number of PTW Data Block is equaled Maximum PTW Data Blocks setted by the host, PTW Buffer Overrun sets and remains set until RESET\_N or SOFT\_RESET\_N goes low.

- 9. Utilized 700 LUT, six 18000-bits RAM blocks. Max Clock is 252 MHz.

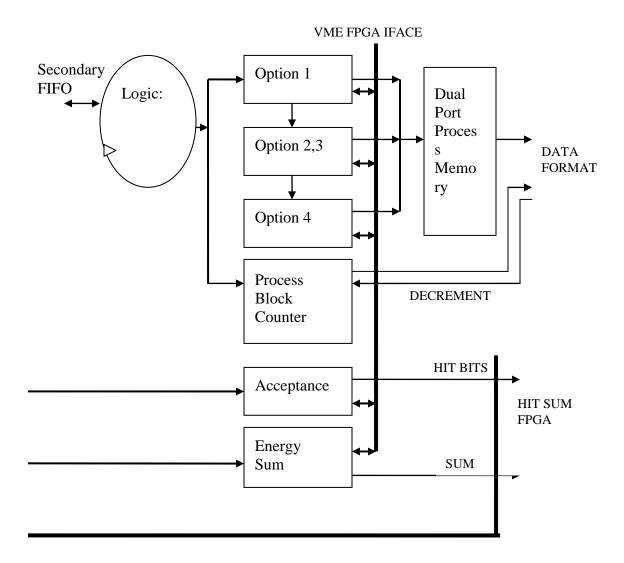

# **Process Algorithms:**

- 1. Read data from Secondary Buffer.

- 2. Parse data to Processing Algorithms

- 3. Process all three options of Data Channel Processing.

- 4. Create Acceptance (Hit bit) pulse

- 5. Compute Energy Sum

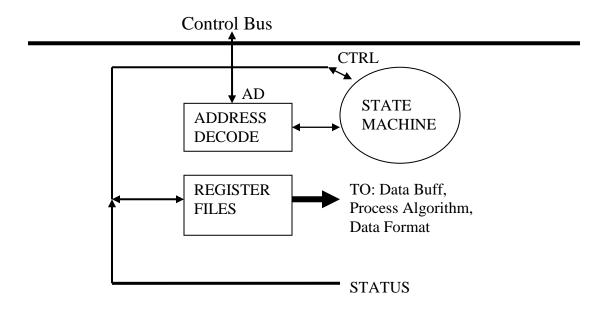

# **VME FPGA IFACE:**

**VHDL Hierarchy**

#### 1. ADC\_PROC\_TOP

- a. SYNC\_ADC\_IN\_VER2

- i. IODELAY

- b. PlayBack\_WV\_Ver2

- i. DPRAM\_16\_1024 (UMEM)

- c. Data\_Buffer\_AllCh\_Ver2\_TOP

- i. Data\_Buffer\_Top (UADCx)

- 1. DP\_RAM1\_TOP (2Kx13) (URAW\_BUFFER\_IN)

- 2. FIFO\_1 (UTrigger\_Buffer)

- 3. DP\_RAM2\_TOP(2Kx17) (UPTW\_DATA\_BUF)

- 4. PTWCPSM

- d. TimeStamp\_TOP

- i. Time\_stamp (Xilinx core gen)

- e. Trigger\_Number\_TOP

- i. Trigger\_number

- f. Processing\_All\_Ver2\_Top

- i. PROCESSING\_TOP (CHx\_PROCESSING)

- 1. DP\_RAM3\_TOP (2Kx18) (UPROCESS\_BUF)

- 2. PROCESSM

- 3. fifo\_12\_64 (UProcAdrHist)

- 4. TDC\_TOP

- a. Linear\_Interpolation (ULI)

- i. Divide\_18By12

#### 1. DIVIDESM

- b. TDCSM

- ii. PROALLSM

- g. DataFormat\_VER2\_TOP

- i. DATFORSM

- h. SUM\_VER2\_TOP (USUM\_TOP)

- i. Hit\_Bit\_All\_ver2\_Top (UHIT\_BITS\_ALL\_TOP)

- i. HIT\_BITS\_TOP (UHIT\_x)

- ii. IOREG\_8bits

#### 2. HOST\_ADCFPGA\_VER2\_TOP

a. HSHOSTSM

## 3. TRIG\_PROC\_TOP

- a. HITBITS\_TOP

- i. ONE\_SHOT

- ii. ONE\_SHOT\_LONG (UTHIT\_WIDTH)

- iii. DELAY\_16bits\_max32clk (UDELAY\_16bits)

- iv. HIT\_WINDOW

- 1. Dpram\_65k\_1

- v. OVERLAP\_WINDOW

- b. SUM\_TRIG

- c. EXT\_FIFO\_WRITE

- i. TRIGGER\_SYNC

- 1. Fifo\_4

ii. EXTFIWRSM

d. HITSUMTOP2 (not connected at FADC250\_V2\_TOP)

VHDL Block Diagram

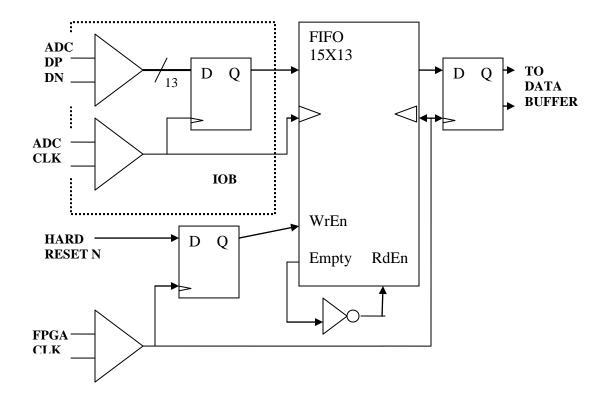

# ADC Input ReSync

Each ADC has 12 bits data, an overflow, and an ADCCLK. The ADC Input Resync captures ADC's data and overflow bits with ADC's output clock to a 15 deep (smallest allow by ISE) by 13 bits FIFO. The FIFO allows the FPGA main CLK to be independent of ADC clock. The FPGA main CLK clocks the data out of FIFO and send to the Data Buffer Block.

The advantage of using ADC's own CLK to capture its data is the elimination of timing variations from ADC to ADC. Moreover, the FIFO Empty signal is used as FIFO Read Enable to allow variation in ADC start up time.

| J                | Primary Memory Map                    |

|------------------|---------------------------------------|

| Address Location | Content                               |

| 0                | ADC Data 0                            |

| 1                | ADC Data 1                            |

| 2                | ADC Data 2                            |

| 3                | ADC Data 3                            |

| 4                | ADC Data 4                            |

| :                | :                                     |

| :                | :                                     |

| :                | :                                     |

| 4078             | ADC Data 4078                         |

| 4079             | ADC Data 4079                         |

| 4080             | ADC Data 4080                         |

| 0                | ADC Data 4081                         |

| 1                | ADC Data 4082                         |

| 2                | ADC Data 4083                         |

| 3                | ADC Data 4084                         |

| :                | :                                     |

| :                | · · · · · · · · · · · · · · · · · · · |

| :                | :                                     |

Data Buffer Primary Memory Man

Primary Memory stores ADC data as it comes in. At the end of buffer, the storing re-circulates and overwrites previous data.

# Data Buffer Secondary Memory Map

| Memory location from<br>beginning of PTW | Content                                                           |

|------------------------------------------|-------------------------------------------------------------------|

| 0                                        | PTW 0 "10010" Trigger Number bits 26-16                           |

| 1                                        | Trigger Number bits 15-0                                          |

| 2                                        | "10011000" Time Stamp bits 47-40                                  |

| 3                                        | Time Stamp bits 39-24                                             |

| 4                                        | "00000000" Time Stamp bits 23-16                                  |

| 5                                        | Time Stamp bits 15-0                                              |

| 6                                        | PTW 0 data 0                                                      |

| :                                        | PTW 0 data 1                                                      |

| :                                        | :                                                                 |

| N-4                                      | "111" PTW <b>0</b> data N-4. "111" indicate almost last data      |

| N-3                                      | PTW <b>0</b> data N-3                                             |

| N-2                                      | PTW <b>0</b> data N-2                                             |

| N-1                                      | PTW <b>0</b> data N-1                                             |

| Ν                                        | PTW 0 last data                                                   |

|                                          |                                                                   |

| N+1                                      | PTW 1 "10010" Trigger Number bits 26-16                           |

| N+2                                      | Trigger Number bits 15-0                                          |

| N+3                                      | "10011000" Time Stamp bits 47-40                                  |

| N+4                                      | Time Stamp bits 39-24                                             |

| N+5                                      | "00000000" Time Stamp bits 23-16                                  |

| N+6                                      | Time Stamp bits 15-0                                              |

| N+7                                      | PTW 1 data 0                                                      |

|                                          | PTW 1 data 1                                                      |

| M-4                                      | :<br>"111" PTW <b>1</b> data M-4. "111" indicate almost last data |

| M-3                                      | PTW 1 data M-4. 111 indicate almost fast data<br>PTW 1 data M-3   |

| M-2                                      | PTW I data M-5<br>PTW 1 data M-2                                  |

| <u>M-1</u>                               | PTW I data M-2<br>PTW I data M-1                                  |

| M                                        | PTW I data M-1<br>PTW I last data                                 |

| 101                                      |                                                                   |

| M+1                                      | PTW 2 "10010" Trigger Number bits 26-16                           |

| M+2                                      | Trigger Number bits 15-0                                          |

| M+3                                      | "10011000" Time Stamp bits 47-40                                  |

| M+4                                      | Time Stamp bits 39-24                                             |

| M+5                                      | "00000000" Time Stamp bits 23-16                                  |

| M+6                                      | Time Stamp bits 15-0                                              |

| M+7                                      | PTW 2 data 0                                                      |

|                                          | PTW 2 data 1                                                      |

|                                          | :                                                                 |

| O-4 | "111" PTW 1 data O-4. "111" indicate almost last data |

|-----|-------------------------------------------------------|

| O-3 | PTW <b>2</b> data O-3                                 |

| O-2 | PTW <b>2</b> data O-2                                 |

| O-1 | PTW <b>2</b> data O-1                                 |

| Ο   | PTW 2 last data                                       |

When a trigger occurs, a number of ADC data words (=PTW\*25MHz) is copied from Primary to Secondary Buffer. The time at which the trigger occurred and the Trigger Number of Bits is included. Since the Number of ADC data words effects where the buffer ended and to minimize gate count, the location of the end of the buffers is provided by the Host Interface block. The Secondary Buffer Size is 2040 to accommodate 4 successive triggers of 2uS PTW (500 locations per trigger).

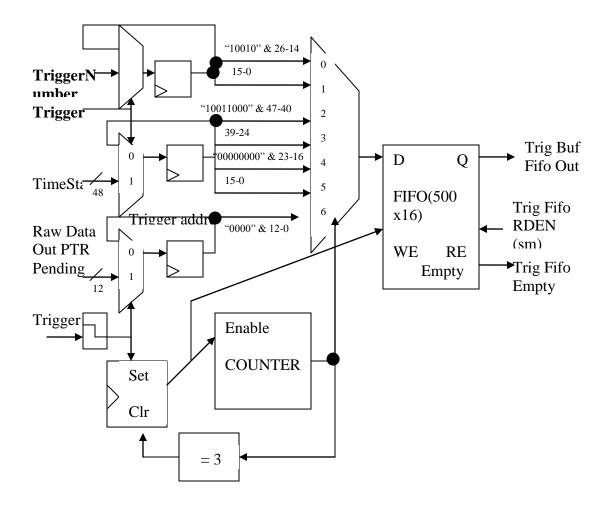

# **Trigger Buffer**

When a trigger occurs, the time stamp and the pointer that points to beginning of Programmable Trigger Window (Raw Data Out PTR Pending) is store to 16 bit FIFO. The 48-bits time stamp is stored in 4 consecutive locations with LSB stored first. Bits 11-0 is padded with "1100" to signify the beginning of PTW window and Time Stamp Words. Bits 23-12, 35-24, and 47-36 are padded with "0100" to signify Time Stamp. After the first word is stored, TrigFifoEmpty goes high and kick off the State Machine to copy time stamp from FIFO to Secondary Dual-Port memory. Data in the PTW stored in the Primary Buffer starting at Trigger Address are copied to Secondary Buffer.

# Data Buffer: Primary and Secondary Buffer

After power up, data from ADC is stored in Ring Buffer continuously. When Trigger is in Trigger Buffer, the Time Stamp is copied from the Trigger Buffer to the Secondary Buffer. The Primary Address when the trigger occurred is retrieved from the Trigger Fifo to be used as the starting Primary address to copy ADC data over. A counter is keeping track of the number of ADC words copied. When the counter equaled the PTW words the copied process stop. Another counter that keeps track of the number of triggers that are in the Secondary Buffer ready for Process algorithm. When a block of trigger is process, this counter is decrement by the Process algorithm.

The Secondary Buffer storage is such that the starting address of each block of trigger data is determine by the PTW but it is fixed with PTW. For example, if PTW is 2uS, the starting address are 0, 504, 1008, 1512. The data formats from low to high address are

```

"1000" "TS bits 47-36"

"1000" "TS bits 35-24"

"1000" "TS bits 23-12"

"1000" "TS bits 11-0"

"010" " TriggerNumber bits 26-14"

"01" " TriggerNumber bits 13-0"

"000" "ADC data"

:

:

"001" "Last ADC data in PTW"

```

PTW Counter is coded such that when decrement commands and increment commands occurs exactly at the same time, decrement occurs before increment.

Data Buffer:

# STATUS

# Data Processing: Memory Map

| Memory location from | Content (WITH EVENT)                   |

|----------------------|----------------------------------------|

| beginning of PTW     |                                        |

| 0                    | "00" "10010" Trigger Number bits 26-16 |

| 1                    | "00" Trigger Number bits 15-0          |

| 2                    | "00" "10011000" Time Stamp bits 47-40  |

| 3                    | "00" Time Stamp bits 39-24             |

| 4                    | "00" "00000000" Time Stamp bits 23-16  |

| 5                    | "00" Time Stamp bits 15-0              |

| 6                    | <b>"00" PTW data 0</b>                 |

| 7                    | <b>"00" PTW data 1</b>                 |

| 8                    | "00" PTW data 2                        |

| 9                    | "00" PTW data 3                        |

| etc                  | etc                                    |

| N+7                  | *"11" "FFFF" : end of PTW              |

|                      |                                        |

| Memory location from | Content (WITHOUT EVENT)                |

| eginning of PTW      |                                        |

| 0                    | "00" "10010" Trigger Number bits 26-16 |

| 1                    | "00" Trigger Number bits 15-0          |

| 2                    | "00" "10011000" Time Stamp bits 47-40  |

| 3                    | "00" Time Stamp bits 39-24             |

| 4                    | "01 "00000000" Time Stamp bits 23-16   |

| 5                    | "01" Time Stamp bits 15-0              |

| 6                    | <b>"01" "0000"</b>                     |

| 7                    | "01" "0000"                            |

| •                    | :                                      |

| •                    | :                                      |

| •                    |                                        |

| N+6                  | N                                      |

N = PTW

| 0                        |                                                 |  |  |  |  |  |  |

|--------------------------|-------------------------------------------------|--|--|--|--|--|--|

| Memory location          | Content (WITH EVENT)                            |  |  |  |  |  |  |

| from beginning of        |                                                 |  |  |  |  |  |  |

| PTW                      |                                                 |  |  |  |  |  |  |

| 0                        | "00" "10010" Trigger Number bits 26-16          |  |  |  |  |  |  |

| 1                        | "00" Trigger Number bits 15-0                   |  |  |  |  |  |  |

| 2                        | "00" "10011000" Time Stamp bits 47-40           |  |  |  |  |  |  |

| 3                        | "00" Time Stamp bits 39-24                      |  |  |  |  |  |  |

| 4                        | "00" "00000000" Time Stamp bits 23-16           |  |  |  |  |  |  |

| 5                        | "00" Time Stamp bits 15-0                       |  |  |  |  |  |  |

| (                        | "10" "0000" Pulse Number "00" SampleNumber from |  |  |  |  |  |  |

| 6                        | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 7                        | "00" PTW pulse 0 data 0                         |  |  |  |  |  |  |

| 8                        | "00" PTW pulse 0 data 1                         |  |  |  |  |  |  |

| Ν                        | "00" PTW pulse 0 data last                      |  |  |  |  |  |  |

| NT 4                     | "10" "0000" Pulse Number "01" SampleNumber from |  |  |  |  |  |  |

| N+1                      | Thredhold bits 9-0                              |  |  |  |  |  |  |

| N+2                      | PTW pulse 1 data 0                              |  |  |  |  |  |  |

| N+3                      | PTW pulse 1 data 1                              |  |  |  |  |  |  |

| M                        | PTW pulse 1 data last                           |  |  |  |  |  |  |

|                          | "10" "0000" Pulse Number "10" SampleNumber from |  |  |  |  |  |  |

| M+1                      | Thredhold bits 9-0                              |  |  |  |  |  |  |

| M+2                      | PTW pulse 2 data 0                              |  |  |  |  |  |  |

| M+2<br>M+3               | PTW pulse 2 data 0                              |  |  |  |  |  |  |

| 0                        | PTW pulse 2 data last                           |  |  |  |  |  |  |

| 0                        | "10" "0000 Pulse Number "11" SampleNumber from  |  |  |  |  |  |  |

| 0+1                      | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 0+2                      | PTW pulse 3 data 0                              |  |  |  |  |  |  |

| 0+2                      | PTW pulse 3 data 1                              |  |  |  |  |  |  |

| P                        | PTW pulse 3 data last                           |  |  |  |  |  |  |

| P+1+7                    | "11" "0000" : end of PTW                        |  |  |  |  |  |  |

| 1+1+/                    |                                                 |  |  |  |  |  |  |

|                          |                                                 |  |  |  |  |  |  |

| Mamanylasstian           | Content (WITHOUT EVENT)                         |  |  |  |  |  |  |

| Memory location          | Content (WITHOUT EVENT)                         |  |  |  |  |  |  |

| from beginning of<br>PTW |                                                 |  |  |  |  |  |  |

|                          | (00) (10010) Trian Number 1:4-26 16             |  |  |  |  |  |  |

| 0                        | "00" "10010" Trigger Number bits 26-16          |  |  |  |  |  |  |

| 1                        | "00" Trigger Number bits 15-0                   |  |  |  |  |  |  |

| 2                        | "00" "10011000" Time Stamp bits 47-40           |  |  |  |  |  |  |

| 3                        | "00" Time Stamp bits 39-24                      |  |  |  |  |  |  |

| 4                        | "01" "00000000" Time Stamp bits 23-16           |  |  |  |  |  |  |

| 5                        | "01" Time Stamp bits 15-0                       |  |  |  |  |  |  |

| 6                        | x"10000"                                        |  |  |  |  |  |  |

| 7                        | x"10000"                                        |  |  |  |  |  |  |

| 8                        | "11" "0000" : end of PTW                        |  |  |  |  |  |  |

## **Data Processing Memory Assignment for Mode 1:**

|                   | nory Assignment for Mode 2:                              |  |  |  |  |  |

|-------------------|----------------------------------------------------------|--|--|--|--|--|

| Memory location   | Content (WITH EVENT)                                     |  |  |  |  |  |

| from beginning of |                                                          |  |  |  |  |  |

| PTW               |                                                          |  |  |  |  |  |

| 0                 | "00" "10010" Trigger Number bits 26-16                   |  |  |  |  |  |

| 1                 | "00" Trigger Number bits 15-0                            |  |  |  |  |  |

| 2                 | "00" "10011000" Time Stamp bits 47-40                    |  |  |  |  |  |

| 3                 | "00" Time Stamp bits 39-24                               |  |  |  |  |  |

| 4                 | "00" "00000000" Time Stamp bits 23-16                    |  |  |  |  |  |

| 5                 | "00" Time Stamp bits 15-0                                |  |  |  |  |  |

| 6                 | "10" "0000" Pulse Number "00" SampleNumber from          |  |  |  |  |  |

| 0                 | Thredhold bits 9-0                                       |  |  |  |  |  |

| 7                 | <b>"00" Pulse 0 Sum bits 18-3</b>                        |  |  |  |  |  |

| 8                 | "00" "0000000000000" Pulse 0 Sum bits 2-0                |  |  |  |  |  |

| 0                 | "10" "0000" Pulse Number "01" SampleNumber from          |  |  |  |  |  |

| 9                 | Thredhold bits 9-0                                       |  |  |  |  |  |

| 10                | <b>"00" Pulse 1 Sum bits 18-3</b>                        |  |  |  |  |  |

| 11                | "00" "000000000000" Pulse 1 Sum bits 2-0                 |  |  |  |  |  |

| 10                | "10" "0000" Pulse Number "10" SampleNumber from          |  |  |  |  |  |

| 12                | Thredhold bits 9-0                                       |  |  |  |  |  |

| 13                | "00" Pulse 2 Sum bits 18-3                               |  |  |  |  |  |

| 14                | "00" "000000000000" Pulse 2 Sum bits 2-0                 |  |  |  |  |  |

| 15                | "10" "0000" Pulse Number "11" SampleNumber from          |  |  |  |  |  |

| 15                | Thredhold bits 9-0                                       |  |  |  |  |  |

| 16                | "00" Pulse 3 Sum bits 18-3                               |  |  |  |  |  |

| 17                | "00" "00000000000" Pulse 3 Sum bits 2-0                  |  |  |  |  |  |

| 18                | "11" "0000" : end of PTW                                 |  |  |  |  |  |

|                   |                                                          |  |  |  |  |  |

| Memory location   | Content (WITHOUT EVENT)                                  |  |  |  |  |  |

| from beginning of |                                                          |  |  |  |  |  |

| PTW               |                                                          |  |  |  |  |  |

| 0                 | "00" "10010" Trigger Number bits 26-16                   |  |  |  |  |  |

| 1                 | "00" Trigger Number bits 15-0                            |  |  |  |  |  |

| 2                 | "00" "10011000" Time Stamp bits 47-40                    |  |  |  |  |  |

| 3                 | "00" Time Stamp bits 17 40<br>"00" Time Stamp bits 39-24 |  |  |  |  |  |

| 4                 | "01" "00000000" Time Stamp bits 23-16                    |  |  |  |  |  |

| 5                 | "01" Time Stamp bits 15-0                                |  |  |  |  |  |

| 6                 | x"10000"                                                 |  |  |  |  |  |

| 7                 | x"10000"                                                 |  |  |  |  |  |

| 8                 | "11" "0000" : end of PTW                                 |  |  |  |  |  |

| <b>U</b>          |                                                          |  |  |  |  |  |

**Data Processing Memory Assignment for Mode 2:**

| 0                 | nory Assignment for Mode 3:                     |  |  |  |  |  |  |

|-------------------|-------------------------------------------------|--|--|--|--|--|--|

| Memory location   | Content (WITH EVENT)                            |  |  |  |  |  |  |

| from beginning of |                                                 |  |  |  |  |  |  |

| PTW               |                                                 |  |  |  |  |  |  |

| 0                 | "00" "10010" Trigger Number bits 26-16          |  |  |  |  |  |  |

| 1                 | "00" Trigger Number bits 15-0                   |  |  |  |  |  |  |

| 2                 | "00" "10011000" Time Stamp bits 47-40           |  |  |  |  |  |  |

| 3                 | "00" Time Stamp bits 39-24                      |  |  |  |  |  |  |

| 4                 | "00" "00000000" Time Stamp bits 23-16           |  |  |  |  |  |  |

| 5                 | "00" Time Stamp bits 15-0                       |  |  |  |  |  |  |

| (                 | "10" "0000" Pulse Number "00" SampleNumber from |  |  |  |  |  |  |

| 6                 | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 7                 | "00" Tfine(50) Vmin (114)                       |  |  |  |  |  |  |

| 8                 | Vmin(30) Vp (110)                               |  |  |  |  |  |  |

| 0                 | "10" "0000" Pulse Number "01" SampleNumber from |  |  |  |  |  |  |

| 9                 | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 10                | "00" Tfine(50) Vmin (114)                       |  |  |  |  |  |  |

| 11                | "00" Vmin(30) Vp (110)                          |  |  |  |  |  |  |

|                   | "10" "0000" Pulse Number "10" SampleNumber from |  |  |  |  |  |  |

| 12                | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 13                | "00" Tfine(50) Vmin (114)                       |  |  |  |  |  |  |

| 14                | "00" Vmin(30) Vp (110)                          |  |  |  |  |  |  |

|                   | "10" "0000" Pulse Number "11" SampleNumber from |  |  |  |  |  |  |

| 15                | Thredhold bits 9-0                              |  |  |  |  |  |  |

| 16                | "00" Tfine(50) Vmin (114)                       |  |  |  |  |  |  |

| 17                | "00" Vmin(30) Vp (110)                          |  |  |  |  |  |  |

| 18                | "11" "0000" : end of PTW                        |  |  |  |  |  |  |

|                   |                                                 |  |  |  |  |  |  |

| Memory location   | Content (WITHOUT EVENT)                         |  |  |  |  |  |  |

| from beginning of |                                                 |  |  |  |  |  |  |

| PTW               |                                                 |  |  |  |  |  |  |

| 0                 | "00" "10010" Trigger Number bits 26-16          |  |  |  |  |  |  |

| 1                 | "00" Trigger Number bits 15-0                   |  |  |  |  |  |  |

| 2                 | "00" "10011000" Time Stamp bits 47-40           |  |  |  |  |  |  |

| 3                 | "00" Time Stamp bits 39-24                      |  |  |  |  |  |  |

| 4                 | "01" "00000000" Time Stamp bits 23-16           |  |  |  |  |  |  |

| 5                 | "01" Time Stamp bits 15-0                       |  |  |  |  |  |  |

| 6                 | x"10000"                                        |  |  |  |  |  |  |

| 7                 | x"10000"                                        |  |  |  |  |  |  |

| 8                 | "11" "0000" : end of PTW                        |  |  |  |  |  |  |

| Ű                 |                                                 |  |  |  |  |  |  |

**Data Processing Memory Assignment for Mode 3:**

## **Data Processing:**

Data Processing for all mode involves scanning the entire secondary buffer. If there is no pulses (data that cross thredshold), x"FFF0" is written to processing memory (PTW) data locations. Trigger Number and Time Stamp info are copied from secondary buffer to processing memory. X"FFF0" signal DataFormat block to prevent data from written to external FIFO. This feature only writes ADC channel that has data that cross threshold (TET).

Data Processing consists of 4 state machines, counters, and pointers. The 4 State Machines include Main and one for each of the 3 Processing Options. When there is ADC data to process, Main State Machine read Time Stamps and Trigger Number from Secondary Buffer and write to Data Processing Buffer. It then calls on one of the other three state machines to process the Option that is in effect.

The state machine for option 1 does the following:

- 1. Copies PTW \* 20MHz number of words from Secondary Data Buffer to Data Processing.

- 2. Increment number of process counter by one

The state machine for option 2 does the following:

- 1. Read ADC data from Secondary Data Buffer. Start PULSE\_TIMER to tick mark the data read.

- 2. If ADC data is above Trigger Threshold, it writes PULSE\_TIMER to Process Buffer. Then it copies NSB and NSA number of words from Secondary Data Buffer to Data Processing Buffer as follow:

- a. If the number of words read before threshold is greater than NSB load RD\_PTW\_PTR with address that is NSB before threshold. If the number of words read (WORD\_AFTER\_TS\_CNT) is less than NSB, load the RD\_PTW\_PTR with address of WORD AFTER TS CNT word back from threshold.

- b. Start NSB\_CNT.

- c. When NSB\_CNT = NSB if WORD\_AFTER\_TS\_CNT > NSB or NSB\_CNT = WORD\_AFTER\_TS\_CNT if WORD\_AFTER\_TS\_CNT < NSB start NSA\_CNT.

- d. When  $NSA_CNT = NSA$ , it stop reading Secondary Buffers.

- 3. Repeat Step 1 and 2 until number (PTW \* 250MHz) numbers of words have been read.

- 4. Write "FFFF" to signal the end of PTW.

5. Increment number of process counter by one

The state machine for option 2 does the following:

- 1. Read ADC data from Secondary Data Buffer.

- 2. If ADC data is above Trigger Threshold, it unable accumulated sum circuit to add ADC value from NSB to NSA ADC words.

- 3. Write accumulated sum to Secondary Data Buffer

- 4. Repeat Step 1, 2, and 3 until number number PTW \* 20MHz numbers of words have been read.

- 5. Write "FFFF" to signal the end of PTW.

6. Increment number of process counter by one

In mode 2 and 3, when the number of words read before the ADC value exceeds the Trigger Threshold is less then NSB, only that many word are processed.

Each state machine is responsible to change and reset the counters that pertained to the option.

The counters and their functions are listed below.

- WORD\_AFTER\_TS\_CNT: keep track of words read from beginning of PTW to the ADC sample that exceeds the Trigger Threshold. If WORD\_AFTER\_TS\_CNT is less then NSB when this Threshold exceeded occurs, the NSB\_PTR\_ENOUGH pointer is used as starting address. Only WORD\_AFTER\_TS\_CNT number of word before Threshold is processed.

- 2. TS\_CNT: keep track of the number of time stamp and trigger number words read from the Secondary Buffer. Main state machine uses this to stop copying time stamp and trigger number words.

- 3. PTW\_WORDS\_CNT: keep track of the number of word in PTW has been read out. It is cleared when it is equaled to number of "PTW words + 4 Time Stamp words + 2 Trigger Number words".

- 4. NSB\_CNT: Keep track of the number of words before Threshold has read and process.

- 5. NSA\_CNT: Keep track of the number of words after Threshold has read and processed.

- 6. PULSE\_TIMER: Tick mark ADC data read from Secondary Buffer from beginning of PTW.

- 7. PULSE\_NUMBER: Keep track of the number of pulses in PTW.

- 8. HOST\_BLOCK\_CNT: Keep track of the number of PTW ready to transfer to host. The host decrement this counter after the host read one PTW.

The pointers and theirs functions are listed below:

- 1. NSB\_PTR\_ENOUGH: This pointer is used as starting address if the number of words read from PTW beginning to Threshold is greater than NSB value. A number of NSB words is processed.

- 2. NSB\_PTR\_NOT\_ENOUGH: This pointer is used as starting address if the number of words read from PTW beginning to Threshold is less than NSB value. Only WORD\_AFTER\_TS\_CNT number of word is processed.

Counters that also serve as pointers are listed below:

RD\_PTW\_PTR: This is the address to the Secondary Buffer. It is load with either NSB\_PTR\_ENOUGH or NSB\_PTR\_NOT\_ENOUGH and increment under state machine control. It is cleared (restart at address 0) when PTW\_WORDS\_CNT is equaled to "number of PTW words + 4 Time Stamp words + 2 Trigger Number words".

#### **TDC Algorithm Overview:**

The TDC algorithm calculates time of the mid value of a pulse relative to the beginning of the look back window. The mid value is the value between the smallest and the peak value of the pulse. The smallest value is the beginning of the pulse. The time consists of coarse time and fine time. The coarse time is the number of clock the sample value before the mid value and the fine time is the interpolating value of mid value away from next sample. The coarse value is 10 bits and the fine value is 6 bit. The resolution of LSB is 1/(CLK \* 64). For a 250MHz the resolution is 62.5 pS. For example for a 20MHz clock, a pulse time value of 110 means the mid-point of the pulse occurred at 6.875nS (62.5pS \* 110) from the beginning of look back window.

### **Requirements for TDC Algorithm:**

ii) There must be at least 5 samples (background) before pulse. Four of these samples are used to determine the pedestal (Vnoise) floor. The minimum value of the pulse is the first value that is Vnoise.

### **TDC Algorithm for Mode 3:**

**1)** Search for Vaverage

- **a)** Latch starting PTW\_RAM ADR

- **b**) Read four samples. Vnoise = Average of 4 samples. Increment sample count by 4.

- **c)** Vmin = Vnoise. Increment sample count.

- **d**) Read until Vram < Vram\_delay. Vpeak = Vram if Vram is greater than TET. Increment sample count.

- e) Store PTW\_RAM ADR for Vpeak.

- **f)** Vaverage = (Vpeak Vmin) / 2

- 2) Search for sample before (Vba) and sample after (Vaa) Vaverage

- **a)** Restore starting PTW\_RAM ADR. Increment Pulse Timer whenever the address is incremented.

- **b**) Read until Vram > Vmin. Vba = Vram

- **c)** Read one more for Vaa

- **d**) Calculated Tfine

- **3)** Write Pulse Number and Pulse Timer to Processing RAM.

- **4)** Increment Pulse Number

- 5) Restore PTW\_RAM ADR for Vpeak. Load sample count to Pulse Timer.

- 6) Read until Vram < Vmin. End of first pulse. Increment Pulse Timer whenever the address is increment. End processing whenever PT\_RAM data is ended.

- **7**) Go to step 1.

## **Data Format :**

Data format read data from Data Processing Memory, put the data in proper format as described in FADC Data Format, and write to external FIFO to host. The data format falls into 5 categories: Event\_Header, Time\_Stamp, Window\_Raw\_Word1, Pulse\_Raw\_Word1, Window\_Pulse\_Raw\_Words\_2\_to\_N, Pulse\_Integral and Event\_Trailer. The words are 36 bits wide.

Event\_Header indicates the start of an event and bits are assigned as follow: (35-34) = 0 (33-32) = 1 (31) = 1 (30-27) = 2(26-0) = trigger number

→ x"19 trigger number"

Trigger Time (Time\_Stamp) indicates time of trigger occurrence relative to the most recent global reset. The six bytes (48 bits) of trigger time Ta Tb Tc Td Te Tf are format in two 32-bits words:

```

Word1:

(35-34) = 0

(33-32) = 0

(31) = 1

(30-27) = 3

(26-24) = 0

(23-16) = Ta

(15-8) = Tb

(7-0) = Tc

\rightarrow x"0980 time stamp hi

Word2:

(35-34) = 0

(33-32) = 0

(31) = 0

(30-24) = 0

(23-16) = Td

(15-8) = Te

(7-0) = Tf

\rightarrow x"0000 time stamp lo

```

Window Raw Word1 indicates the beginning of Window Raw Data.

(35-34) = 0 (33-32) = 0 (31) = 1 (30-27) = 4(26-23) = Channel number (0-7) (22-12) = 0

(11-0) = Window Width (PTW) (in number of samples).

→ x"0A ChannelNumber 00 numberOfSamples"

3322 2222 2222 1111 1111 1198 7654 3210 1098 7654 3210 9876 5432 10

1010 0Cha n000 0000 0000 Ptw- ----

Pulse Raw Word1 indicates the beginning of Pulse Raw Data.

(35-34) = 0 (33-32) = 0 (31) = 1 (30-27) = 6 (26-23) = Channel number (0-7) (22-21) = pulse number (0-3) (20-10) = 0 (9-0) = time from beginning of PTW that the pulse crossed thredshold → x"0B ChannelNumber 00 TIME"

3322 2222 2222 1111 1111 1198 7654 3210 1098 7654 3210 9876 5432 10 1011 0Cha nP#0 0000 0000 00Ti me-- ----

Remaining words for Pulse Raw Data and Window Raw Data have the same format.

(35-34) = 0 (33-32) = 0 (31) = 0 (30) = 0 (29) = 1 indicates sample x not valid (28-16) = ADC sample x (includes overflow bit) (15-14) = 0 (13) = 1 indicates sample x+1 not valid. (12-0) = ADC sample x+1 (includes overflow bits).

3322 2222 2222 1111 1111 1198 7654 3210 1098 7654 3210 9876 5432 10

00xA dcSa mple ---- 00xA dcSa mple ----

**Pulse Time** (8) – time associated with an identified pulse within the trigger window. (31) = 1 (30 - 27) = 8 (26 - 23) = channel number (0 - 15) (22 - 21) = pulse number (0 - 3)

(20 - 19) = measurement quality factor (0 - 3)

(18 - 16) = reserved (read as 0)

(15 - 6) = coarse pulse time

(5 - 0) = fine pulse time

3322 2222 2222 1111 1111 1198 7654 3210

1098 7654 3210 9876 5432 10

\_\_\_\_\_

1100 0Cha nP#0 0000 Puls eTim e

**Pulse Integral** (7) – integral of an identified pulse within the trigger window. The pulse integral may be a simple sum of raw data samples over the pulse duration, or the result of a complex fit to pulse shape. Pedestal subtraction may be included.

```

(31) = 1

(30-27) = 7

(26-23) = \text{channel number } (0-15)

(22-21) = \text{pulse number } (0-3)

(20-19) = \text{measurement quality factor } (0-3)

(18-0) = \text{pulse integral}

3322\ 2222\ 2222\ 1111\ 1111\ 1198\ 7654\ 3210

1098\ 7654\ 3210\ 9876\ 5432\ 10

-------

1011\ 1\text{Cha nP#0}\ 0\text{Pul seIn tegral}

```

**Pulse Vmin Vpeak** (10) – ADC count for minimum and peak value of a pulse. This is too be used off line to apply correction to Pulse Time in TDC mode.

(31) = 1 (30 - 27) = 10 (26 - 23) = channel number (0 - 15) (22 - 21) = pulse number (0 - 3) (20 - 12) = Vmin (11 - 0) = Vpeak  $3322 \ 2222 \ 2222 \ 1111 \ 1111 \ 1198 \ 7654 \ 3210$   $1098 \ 7654 \ 3210 \ 9876 \ 5432 \ 10$  $1101 \ 0\text{Cha nP#v minn nnn vpea kkkk kkkk}$

Event Trailer: Indicate the end of an event. EVENT\_TRAILER = "0010" & X"E8000000"; Example:

Raw Data (mode0) :

x"19\_\_\_\_" Event Header

x"98\_\_\_\_ " Time Stamp upper 24 bits.

x"\_\_\_\_\_" Time Stamp lower 24 bits.

x"A\_\_\_\_\_" Channel Number, Window Width (PTW)

x"\_\_\_\_" Raw Data

x"2E8000000" End of Event

Pulse Data (mode 1):

x"19\_\_\_\_" Event Header

x"98 " Time Stamp upper 24 bits.

x"\_\_\_\_\_" Time Stamp lower 24 bits.

x"B\_\_\_\_\_" ChanNum(26-23), PulseNumb(22-21), Time from beginning of PTW that the pulse crossed thredshold(9-0).

x" 2 pulses (12-0) (28-16) per 36 bits words.

x"2E8000000" End of Event

Pulse Sum (mode 2):

x"19\_\_\_\_" Event Header

x"98\_\_\_\_\_ " Time Stamp upper 24 bits.

x"\_\_\_\_\_" Time Stamp lower 24 bits.

x"C\_\_\_\_\_" Pulse time, ChanNum(26-23), PulseNumb(22-21), Time(15-0)

x"B8\_\_\_\_" Channel Numbe(26-23)r, Pulse Number(22-21), Pulse Integral (18-0)

x"2E8000000" End of Event

TDC (mode 3):

x"19\_\_\_\_" Event Header

x"98\_\_\_\_\_ " Time Stamp upper 24 bits.

x"\_\_\_\_\_" Time Stamp lower 24 bits.

x"C\_\_\_\_\_" Pulse time, ChanNum(26-23), PulseNumb(22-21), Time(15-0)

x"D\_\_\_\_\_" ChanNum(26-23), PulseNumb(22-21), Vm(20-12), Vp(11-0)

x"2E8000000" End of Event

Raw Data and TDC (mode 7)

x"19\_\_\_\_" Event Header

x"98\_\_\_\_\_ " Time Stamp upper 24 bits.

x"\_\_\_\_\_" Time Stamp lower 24 bits.

x"A\_\_\_\_\_" Channel Number, Window Width (PTW)

x"\_\_\_\_" Raw Data

x"C\_\_\_\_" Pulse time

x"D\_\_\_\_" VminVpeak

x"2E8000000" End of Event

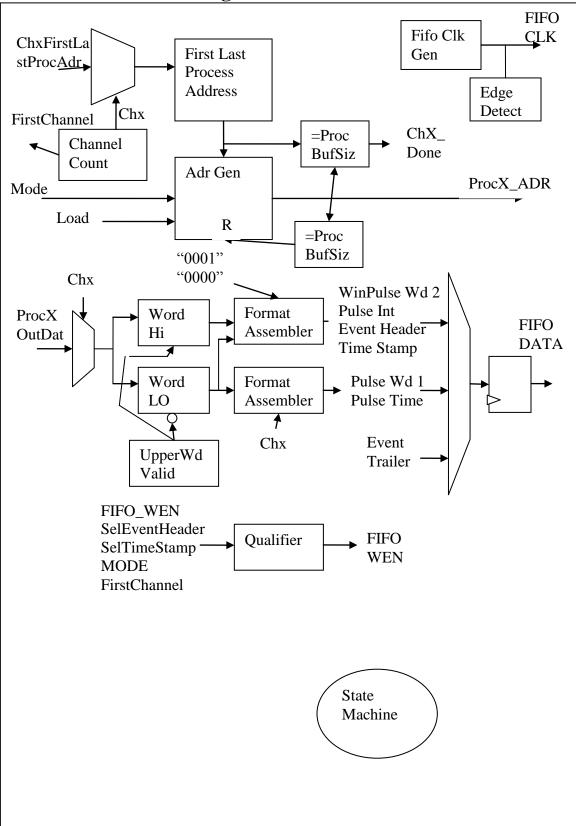

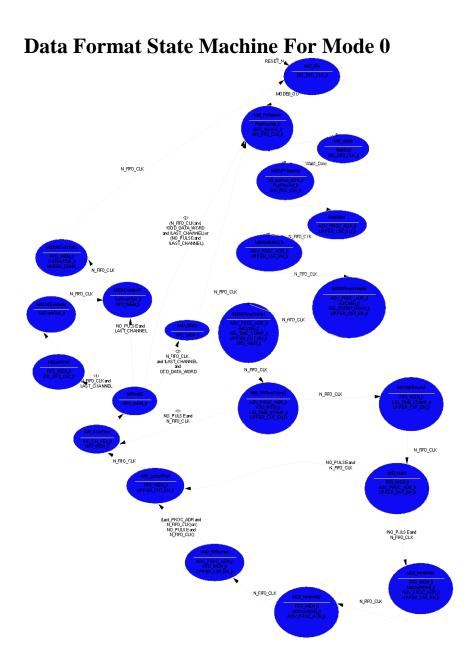

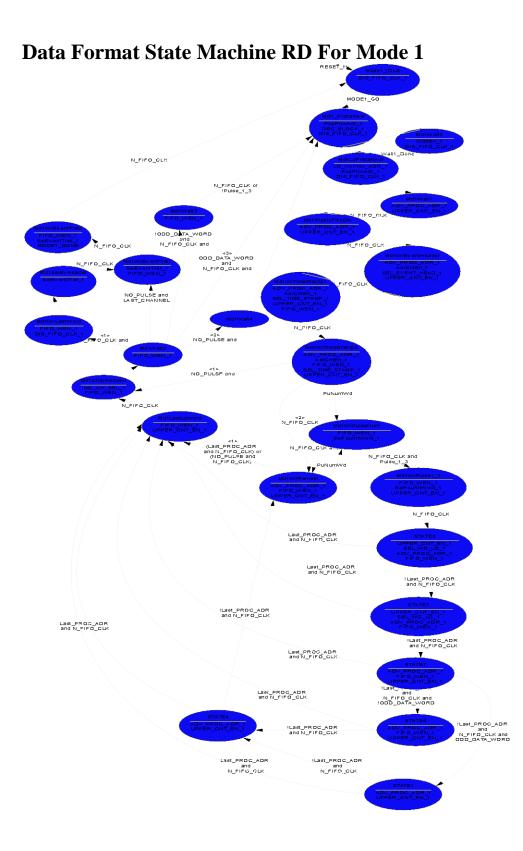

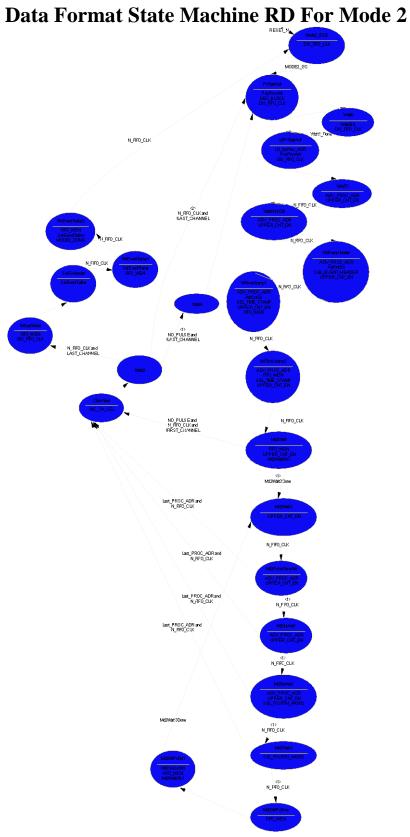

## **Data Format VHDL:**

The VHDL code read data streams from processing block, format them per document "FADC Data Format" by Ed Jastrzembski.

When all HOST\_BLOCKx\_CNT is greater then one, DATFORSM begins the write out algorithm. The algorithm is as follow:

1) Pop the starting and last address of the data in the processing buffer.

2) Load the starting adddress of Channel 0 to Address counter. Start FIFO clock. Inc Address counter on rising edge of FIFO clock.

Output Address to PROCx\_ADR

3) Read data from PROCx\_OUTDAT. Assemble them into Event Header, TimeStamp1, and TimeStamp2 and writes to FIFO.

4) In mode 0, the Address is stop after TimeStamp2 address (5) to allow time to insert Window Raw Data Word 1 which contains Channel Number and Window Width.

5) In mode 1 and mode 2, the Address is stop after Pulse Number and SampleNumber from Threshold Address (6), to allow time to assemble Pulse Raw Data Word 1 which contains Channel Number and

first sample number for pulse or Pulse Time which contains Channel Number and pulse time.

6) The data are read and write in pairs until the Address counter equal last address of the processing buffer. The channel are incremnent and repeats step 1 through 6.

7) After the last channel is finish, Event Trailer is written to FIFO.

Because of the different in the data format between the modes: 0,1,and 2, each mode has its own state machine.

In mode 2, there might be extra words (for some setting of NSA and NSB) in the processing buffer after the last integral, the statemachine does not write this to FIFO. In mode 0 and 1, for even number of data, the number of data written to FIFO is 2 more, for odd number of data, the number of data written to FIFO is one more.

Data Streams from Processing for diferent modes:

In mode 0: EventHeader, TimeStamp1, TimeStamp2, WindowRaw(not from processing), Deven Dodd,..., TimeEnd

In mode 1: EventHeader, TimeStamp1, TimeStamp2, PulseRaw(upper 16 from processing, not lower 16), Deven Dodd,..., TimeEnd

In mode 1: EventHeader, TimeStamp1, TimeStamp2, PulseRaw(upper 16 from processing, not lower 16), Integral, TimeEnd

**Data Format VHDL Diagram**

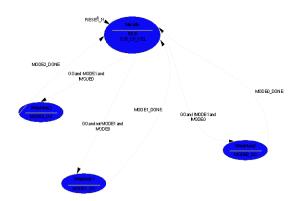

# **Data Format State Machine Main**

Main State Machine does the following:

**1.** Call State Machine for Mode 0,1,or 2.

# SUM

# HIT BITS

-

**<u>VME FPGA IFACE:</u>** Control Bus Memory Map for FADC FPGA

| Control Bus Memory N | -               |              |        | Drimer                                           | Eurotion                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|-----------------|--------------|--------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                 | Width<br>(Bits) | Quant<br>ity | Access | Primary<br>Address<br>(Secondar<br>y<br>Address) | Function                                                                                                                                                                                                                                                                                                                                                                                                             |

| STATUS0              | 16              | 1            | R      | 0x0000<br>()                                     | Bits 14 to 0: Code<br>Version<br>Bit 15: 1= Command<br>can be sent to AD9230                                                                                                                                                                                                                                                                                                                                         |

| STATUS1              | 16              | 1            | R      | 0x0001<br>()                                     | TRIGGER NUMBER<br>BIT 15 to 0                                                                                                                                                                                                                                                                                                                                                                                        |

| STATUS2              | 16              | 1            | R      | 0x0002<br>()                                     | Tbd. Read 0                                                                                                                                                                                                                                                                                                                                                                                                          |

| CONFIG 1             | 16              | 1            | R/W    | 0x0003<br>()                                     | Bit 0-2 (process mode):<br>$000 \rightarrow$ Select option1<br>$001 \rightarrow$ Select option2<br>$010 \rightarrow$ Select option3<br>$011 \rightarrow$ Select option4<br>$111 \rightarrow$ Run option1<br>then option4 for each<br>trigger<br>Bit 3: 1:Run<br>Bit 6-5 : Number of<br>Pulses in Mode 1 and 2<br>Bit 7: Test Mode (play<br>Back).                                                                    |

| CONFIG 2             |                 |              | R/W    | 0x0004<br>()                                     | When 1 ADC values = 0<br>Bit $0 \rightarrow ADC 0$<br>Bit $1 \rightarrow ADC 1$<br>Bit $2 \rightarrow ADC 2$<br>Bit $3 \rightarrow ADC 3$<br>Bit $4 \rightarrow ADC 4$<br>Bit $5 \rightarrow ADC 5$<br>Bit $6 \rightarrow ADC 6$<br>Bit $7 \rightarrow ADC 7$<br>Bit $8 \rightarrow ADC 8$<br>Bit $9 \rightarrow ADC 9$<br>Bit $10 \rightarrow ADC 10$<br>Bit $11 \rightarrow ADC 11$<br>Bit $12 \rightarrow ADC 12$ |

| <b></b>  | Т  | r | T      | 1      |                                      |

|----------|----|---|--------|--------|--------------------------------------|

|          |    |   |        |        | Bit $13 \rightarrow ADC 13$          |

|          |    |   |        |        | Bit $14 \rightarrow ADC 14$          |

|          |    |   |        |        | Bit $15 \rightarrow ADC 15$          |

|          |    |   |        |        |                                      |

| CONFIG 4 | 16 | 1 | 1      | 0x0005 | $7 \Rightarrow$ rising edge write to |

|          |    |   |        |        | AD9230 ADC                           |

|          |    |   |        |        | $6 \Rightarrow 1$ write to all ADC.  |

|          |    |   |        |        | Bits 30 are don't care               |

|          |    |   |        |        |                                      |

|          |    |   |        |        | $5 \Rightarrow 0$ write to AD9230    |

|          |    |   |        |        | 1 read from                          |

|          |    |   |        |        | AD9230                               |

|          |    |   |        |        | $30 \Rightarrow$ Select ADC to       |

|          |    |   |        |        | write to                             |

| CONFIG 5 | 16 | 1 |        | 0x0006 | $158 \Rightarrow$ Registers inside   |

|          |    |   |        |        | AD9230                               |

|          |    |   |        |        | $70 \Rightarrow$ Data to write to    |

|          |    |   |        |        | register.                            |

| PTW      | 9  | 1 | R/W    | 0x0007 | Number of ADC sample                 |

| 1 1 **   |    | 1 | 1\/ \\ | ()     | to include in trigger                |

|          |    |   |        | ()     | window.                              |

|          |    |   |        |        |                                      |

|          |    |   |        |        | PTW = Trigger Window                 |

|          |    |   |        |        | (ns) * 250 MHz.                      |

|          |    |   |        |        | Minimum is 6.                        |

|          |    |   |        |        | Always report Even                   |

|          |    |   |        |        | Number. For odd PTW                  |

|          |    |   |        |        | number, discard the                  |

|          |    |   |        |        | last sample reported.                |

| PL       | 11 | 1 |        | 0x0008 | Number of sample back                |

|          |    |   |        | ()     | from trigger point.                  |

|          |    |   |        |        | PL = Trigger                         |

|          |    |   |        |        |                                      |

| NCD      | 10 | 1 |        | 00000  | Window(ns) * 250MHz                  |

| NSB      | 12 |   |        | 0x0009 | Number of sample                     |

|          |    |   |        | ()     | before trigger point to              |

|          |    |   |        |        | include in data                      |

|          |    |   |        |        | processing. This include             |

|          |    |   |        |        | the trigger Point.                   |

|          |    |   |        |        | Minimum is 2 in all                  |

|          |    |   |        |        | mode.                                |

| NSA      | 13 | 1 |        | 0x000A | Number of sample after               |

|          |    |   |        | ()     | trigger point to include             |

|          |    |   |        |        | in data processing.                  |

|          |    |   |        |        | Minimum is (6 in mode                |

|          |    |   |        |        | 2)and (3 in mode 0                   |

|          |    |   |        |        |                                      |

|          |    |   |        |        | and 1). Number of                    |

|          |    |   |        |        | sample report is 1                   |

|          |    |   |        |        | more for odd and 2                   |

|                |     |     |        |          | more for even NSA         |

|----------------|-----|-----|--------|----------|---------------------------|

|                | 10  | 1.6 |        | 0.0005   | number.                   |

| TET            | 12  | 16  |        | 0x000B - | Trigger Energy            |

|                |     |     |        | 0x001A   | Thredhold.                |

| PTW DAT BUF    | 12  | 1   |        | 0x001B   | Last Address of the       |

| LAST ADR       |     |     |        |          | Secondary Buffer. See     |

|                |     |     |        |          | calculation below         |

| PTW MAX BUF    | 8   | 1   |        | 0x001C   | The maximum number        |

|                |     |     |        |          | of unprocessed PTW        |

|                |     |     |        |          | blocks that can be stored |

|                |     |     |        |          | in Secondary Buffer.      |

|                |     |     |        |          | See Calculation below.    |

| Test Wave Form | 16  | 1   |        | 0x001D   | Write to PPG. Read        |

|                |     |     |        |          | should immediately        |

|                |     |     |        |          | follow write.             |

| ADC0 Pedestal  | 16  | 1   | R/W    | 0x001E   | Subtract from ADC0        |

| Subtract       |     |     |        |          | Count before Summing      |

| ADC1 Pedestal  | 16  | 1   | R/W    | 0x001F   | Subtract from ADC1        |

| Subtract       |     |     |        |          | Count before Summing      |

| ADC2 Pedestal  | 16  | 1   | R/W    | 0x0020   | Subtract from ADC2        |

| Subtract       |     |     |        |          | Count before Summing      |

| ADC3 Pedestal  | 16  | 1   | R/W    | 0x0021   | Subtract from ADC3        |

| Subtract       |     |     |        |          | Count before Summing      |

| ADC4 Pedestal  | 16  | 1   | R/W    | 0x0022   | Subtract from ADC4        |

| Subtract       |     |     |        |          | Count before Summing      |

| ADC5 Pedestal  | 16  | 1   | R/W    | 0x0023   | Subtract from ADC5        |

| Subtract       | 10  | -   |        | 0110020  | Count before Summing      |

| ADC6 Pedestal  | 16  | 1   | R/W    | 0x0024   | Subtract from ADC6        |

| Subtract       | 10  | -   |        | 0110021  | Count before Summing      |

| ADC7 Pedestal  | 16  | 1   | R/W    | 0x0025   | Subtract from ADC7        |

| Subtract       | 10  | -   |        | 0110020  | Count before Summing      |

| ADC8 Pedestal  | 16  | 1   | R/W    | 0x0026   | Subtract from ADC8        |

| Subtract       | 10  | 1   | 10     | 0110020  | Count before Summing      |

| ADC9 Pedestal  | 16  | 1   | R/W    | 0x0027   | Subtract from ADC9        |

| Subtract       | 10  | 1   | 10 11  | 010027   | Count before Summing      |

| ADC10 Pedestal | 16  | 1   | R/W    | 0x0028   | Subtract from ADC10       |

| Subtract       | 10  | 1   | 10/ 11 | 0X0020   | Count before Summing      |

| ADC11 Pedestal | 16  | 1   | R/W    | 0x0029   | Subtract from ADC11       |

| Subtract       | 10  | 1   | 11/ 11 | 0X0027   | Count before Summing      |

| ADC12 Pedestal | 16  | 1   | R/W    | 0x002A   | Subtract from ADC12       |

| Subtract       | 10  | 1   | 11/ 11 | 0A002A   | Count before Summing      |

| ADC13 Pedestal | 16  | 1   | R/W    | 0x002B   | Subtract from ADC13       |

| Subtract       | 10  | 1   | IX/ VV | 0X002D   |                           |

|                | 16  | 1   | D/W/   | 0x002C   | Count before Summing      |

| ADC14 Pedestal | 16  | 1   | R/W    | 0x002C   | Subtract from ADC14       |

| Subtract       | 1.0 | 1   |        | 0002D    | Count before Summing      |

| ADC15 Pedestal | 16  | 1   | R/W    | 0x002D   | Subtract from ADC15       |

| Subtract               |    |    |     |                           | Count before Summing                                                                                                                                                                                                                                                                                                                           |

|------------------------|----|----|-----|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |    |    |     |                           |                                                                                                                                                                                                                                                                                                                                                |

| STATUS3                | 16 | 1  | R   | 0x0400<br>()              | 00                                                                                                                                                                                                                                                                                                                                             |

| CONFIG6                | 16 | 1  | R/W | 0x0401<br>()              | 00→ Table mode10→ Window mode01→ Boolean Overlap11→ undefinedBit 2: 0→ T_HIT to CtrlFPGA, Hitpattern toFIFO1→ T_SUM toCtrl FPGA, Sumpatternto FIFOBitt3: 1→ select Hit Bitwith programmablepositive pulse width toP2.Bit4 0→ unable Tableoverlap and Triggermode1→ read back hitpattern selection table.Disable Table overlapand Trigger mode. |

| HITBITS_WIDTH          | 8  | 16 | R/W | 0x0402<br>(0 –<br>0x000F) | (70) Hit Bits One Shot<br>Pulse Width. Actual<br>width is one clk longer.                                                                                                                                                                                                                                                                      |

| HITS_DLY               | 16 | 1  | R/W | 0x0403                    | Actual delay is 7 clock<br>longer for all values.<br>Exmple: $0 \rightarrow 7$ , $1 \rightarrow 8$ ,<br>$2 \rightarrow 9$ etc. Delay is from<br>input of FX20.                                                                                                                                                                                 |

| Live Trig Out<br>WIDTH | 8  | 1  | R/W | 0x0404                    | Pulse width of LiveTrig<br>Output. Actual width is<br>1 clock longer.                                                                                                                                                                                                                                                                          |

| TRIGGER HITBITS        | 16 | 1  | R/W | 0x0405                    | In Window Mode.<br>Select Hit Bit(s) that can                                                                                                                                                                                                                                                                                                  |

|                                        |    |       |     |        | activate(s) window. The<br>Bit(s) that activate the<br>Window is include in<br>the Trigger Hit Pattern.                               |

|----------------------------------------|----|-------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| WINDOW WIDTH                           | 16 | 1     | R/W | 0x0406 | In Window Mode.<br>Select the duration of<br>window. Width is 2<br>clock longer.                                                      |

| BOOLEAN<br>OVERLAP<br>QUALIFIED BITS   | 16 | 1     | R/W | 0x0407 | In Boolean Overlap<br>Mode. Select Hit Bits to<br>be active in this mode                                                              |

| HIT PATTERN<br>SELECTION TABLE<br>DATA | 16 | 65536 | R/W | 0x0408 | Write to 65536x1 Hit<br>Pattern Selection Table.<br>Each word contains data<br>for 1 location. The<br>address are auto-<br>increment. |

| SUM/HITBIT<br>External FIFO            | 16 |       | R   | 0x0409 | Read HITBITS                                                                                                                          |

| SUM Threshold                          | 16 | 1     | R/W | 0x40A  | Write SUM Threshold<br>Register. T_SUM goes<br>high when BSUM ><br>register value                                                     |

### PTW MAX BUF = INT(2016 / (PTW + 8) \* 25000000)

Where:

2016  $\rightarrow$  Number of address of Secondary Buffer PTW  $\rightarrow$  Trigger Window width in nano-second

## PTW DAT BUF LAST ADR = PTW MAX BUF \* (PTW + 6)-1;

Where:

6  $\rightarrow$  4 address for Time Stamp and 2 address for Trigger Number NumberOfBytePerTrigger  $\rightarrow$  PTW \* 250 MHz.