### Update/Status for NPS HV, Electronics, DAQ

Brad Sawatzky

NPS Collaboration Meeting Feb 3, 2020

### **Needed Readout Hardware for NPS**

### • NPS: 1080 PbWO<sub>4</sub> blocks

- $\rightarrow$  Readout consists of JLab F250 FADCs

- » Full waveform for crystals of interest

- » < 1ns timing res. is provided by F250s

- $\rightarrow$  NPS trigger generated by JLab VTP modules in NPS F250 VXS crates

### Hardware needed for NPS

- $\rightarrow$  67x FADCs

- $\rightarrow$  5x VXS crates

- $\rightarrow$  5x SD + TI + Linux SBC / ROC

- $\rightarrow$  5x VTP modules

### • Firmware development

- $\rightarrow$  VTP firmware updated to provide required summing trigger

- $\rightarrow$  TI/TM firmware modified to support full complement of 5 NPS crates + 3 HMS crates

- NOTE: VTP firmware trigger latency is NOT a problem

- $\rightarrow$  All HMS modules (F250s, CAEN 1190s) have deep lookback buffers

- $\rightarrow$  HMS pre-trigger(s) will be delayed to meet VTP trigger

### **Needed Readout Hardware for NPS**

### NPS: 1080 PbWO<sub>4</sub> blocks

- → Readout consists of JLab F250 FADCs

- » Full waveform for crystals of interest

- » < 1ns timing res. is provided by F250s

- → NPS trigger generated by JLab VTP modules in NPS F250 VXS crates

### • Hardware needed for NPS

- $\rightarrow$  67x FADCs

- $\rightarrow$  5x VXS crates

- $\rightarrow$  5x SD + TI (+4 ordered Fall '19)

- $\rightarrow$  5x Linux SBC / ROC

- $\rightarrow$  5x VTP modules

### • Firmware development

- $\rightarrow\,$  VTP firmware updated to provide required summing trigger

- → TI/TM firmware modified to support full complement of 5 NPS crates + 3 HMS crates

- NOTE: VTP firmware trigger latency is NOT a problem

- → All HMS modules (F250s, CAEN 1190s) have deep lookback buffers

- $\rightarrow$  HMS pre-trigger(s) will be delayed to meet VTP trigger

Thomas Jefferson National Accelerator Facility

#### NPS Collab. Meeting • Feb 3, 2020

### Still needed!

- $\rightarrow\,$  Energy / ADC / Timing:

- » +51x FADCs (\*)

- » +2-3x VXS crates

- » +5x SBC (+spare)

- → FPGA NPS trigger

- » +5x VTP (+ spare)

- → Addl MTP fiber 'DAQ' trunk line SHMS  $\leftrightarrow$  CH (*if needed*)

- → Upgrade network switches in SHMS and CH to 10 gigE (JLab CNI support)

- VXS Crates and support modules are in the Hall C purchase plan/schedule

- (\*) F250s provided by Physics Division/ Fast Electronics group

- → Pre-existing Lab inventory

- → <u>Must ensure they are reserved</u> <u>for NPS installation+running</u>

- » Contention w/ SBS?

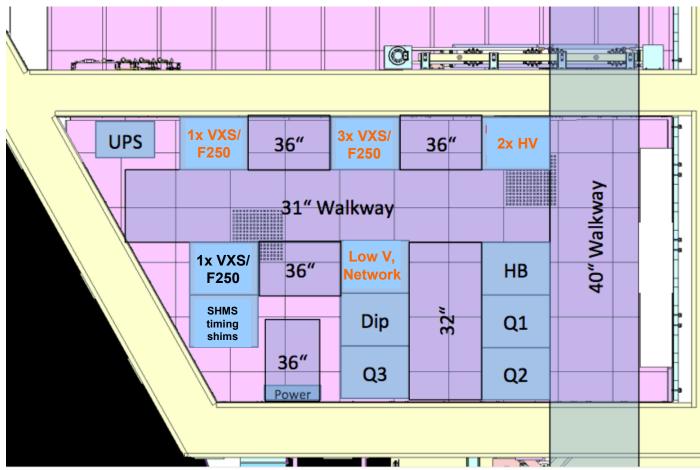

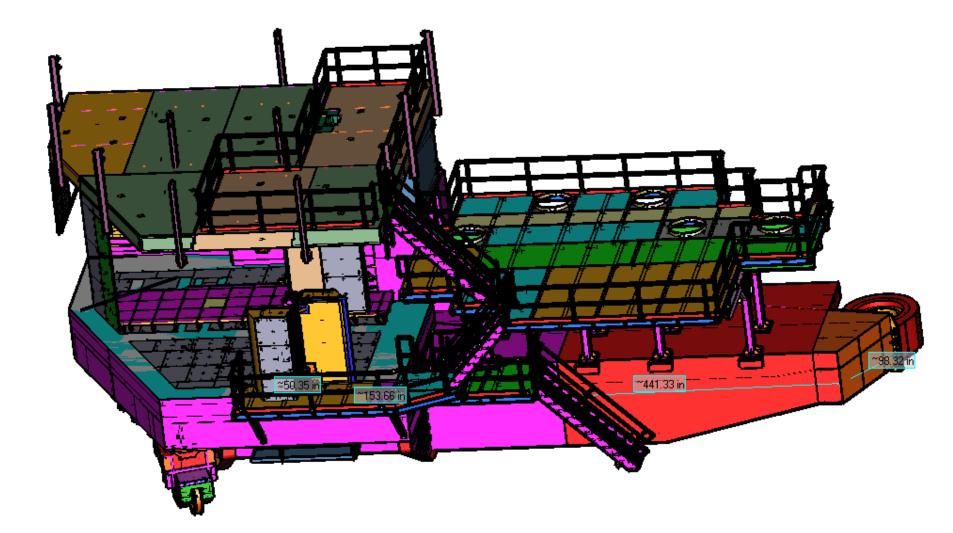

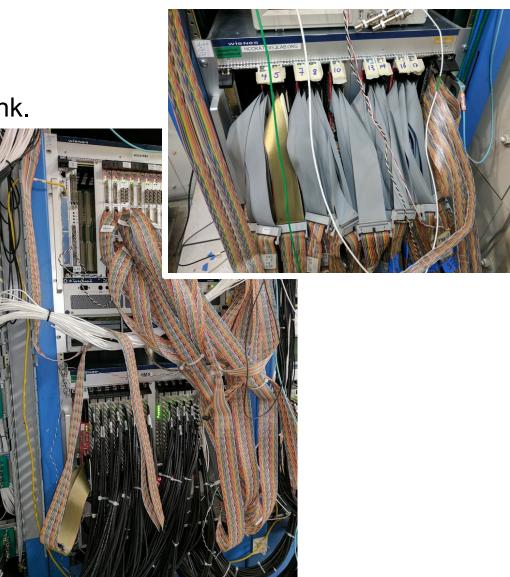

### **Rackspace in SHMS hut**

- 4+1 VXS crates + 2 High Voltage crates

- $\rightarrow$  It's pretty snug, but it'll fit...

- $\rightarrow$  Cables flow into crates via cable trays running above racks

Thomas Jefferson National Accelerator Facility NPS Collab. Meeting • Feb 3, 2020

# **NPS DAQ Challenges**

- Most work driven by requirement to handle highrate kinematics + waveform output

- $\rightarrow$  13 kHz HMS (DIS) triggers (+ background)

- » need NPS trigger ( $\rightarrow$  VTP firmware)

- » need 'Event-Blocking' enabled

- $\rightarrow$  'high' multiplicity in NPS (75+ crystals)

- $\rightarrow$  waveform output for participating crystals is a 'Must' (~25 samples/ch)

- Pending issues

- $\rightarrow$  VTP firmware development

- » 3x3 crystal cluster triggers

- Updated (15 May 2019) Emit logic-out for NIM trigger with HMS »

- » 'sparsify' F250 readout (only store 4 waveforms from 5x5 clusters centered on 3x3 'trigger' cluster)

- $\rightarrow$  Analyzer support for VTP payload

- $\rightarrow$  Analyzer support for Event-Blocking mode

- » 'Unblock' in secondary ROL?

- may be simplest? no analyzer changes needed [Moffit?]

- » 'Unblock' at analyzer? [Bob M]

Thomas Jefferson National Accelerator Facility

NPS Collab. Meeting • Feb 3, 2020

- Firmware questions wrt VTP/F250s

- $\rightarrow$  Hall B firmware has compression, but removes features to achieve this

- need to ensure necessary timing, » QDC, scaler(?) data still present

- $\rightarrow$  May require upgrading HMS F250 firmware as well

- need to address knock-on » changes to CRLs and analyzer assumptions for HMS

- $\rightarrow$  <u>Or</u> lossless compression in 2<sup>nd</sup> stage ROL + libCoda mod?

- no F250 firmware change, no » decoder changes

- Firmware / DAQ questions have been discussed with FE Group

- $\rightarrow$  No "show-stoppers" but requires development resources be allocated to this project

- Updates to Hall C analyzer software

- → Non-trivial work here!

# VTP/F250/TM Firmware / Trigger

- VTP (5+1 modules attached to next FE order)

- $\rightarrow$  Cluster trigger based on 3x3 groups, with 1 row shared between crates

- $\rightarrow$  Logic signals emitted by each VTR will be OR'd in NIM to form NPS trigger

- » CODA trig: HMS .AND. (.OR. of NPS)

- Timing latency on VTP triggers deterministic to <12ns

- → Define/update VTP data payload

- » cluster charge, timing?

- Updated (15 May 2019) » cluster crystal list to be used to sparsify F250 waveform readout

- F250 FADC (51 modules from FE/PD pool)

- $\rightarrow$  Hi-res timing required (< 1ns)

- » Preserve multi-hit/ch output

- $\rightarrow$  QDC data, Scaler data

- $\rightarrow$  Full waveforms (25 samples)

- » Compressed?

- $\rightarrow$  VTP info used to sparsify F250 readout channels to those in a 5x5 cluster(s) centered on the 3x3 'trigger' cluster(s)

- **TI/TM modifications**

- $\rightarrow$  must support 5 NPS crates + 3 HMS crates

- Modified layout with multiple TMs »

- $\rightarrow$  maintain six L1 trigger inputs on primary TM

- **CODA** assumptions

- → Will need FE support for 'new' Vivo VME interface chip on Intel SBCs

- to be purchased for NPS crates »

- 'Standard HMS' NIM triggers will be available

- » <sup>3</sup>/<sub>4</sub>, EL<sub>real</sub>, EL<sub>clean</sub>, ...

- → NPS + HMS trigger made in NIM

- » NPS + HMS  $\{\frac{3}{4}, EL_{for}\}$

- NPS VTP latency is NOT a problem »

FE development requests submitted to C. Cuevas for planning/approval

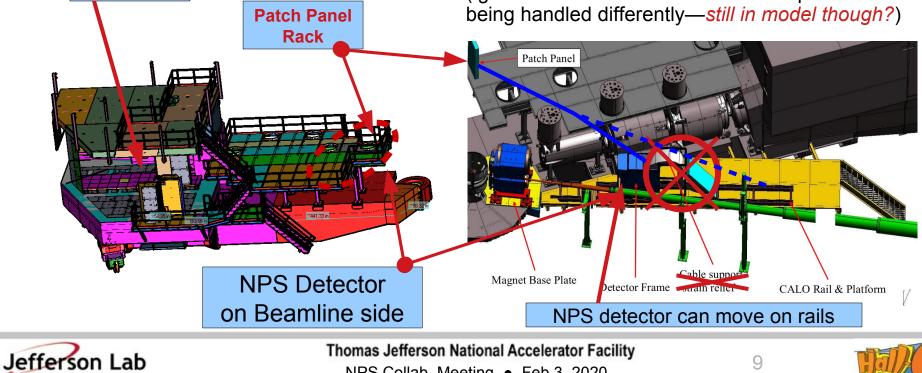

# Signal/HV Cable Runs

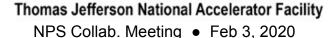

- Plan is for a single 84" tall, 19" standard width rack to be placed near the pivot

- → Planned to go on the upper, power supply deck

- The rack at the pivot will be "double sided":

- → One side will provide 1100 BNC connections

- » BNC ↔ BNC feedthroughs

- → Other side provides 30+2 high-density HV connections

- » Connector TBD

- \$\$/avail. issues

- » 36 ch/connector

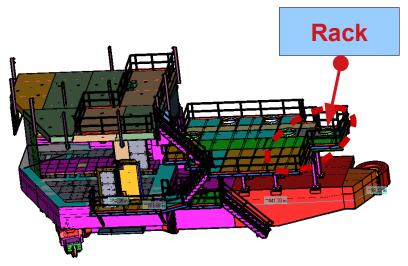

## **BNC Patch Notes**

- BNC patch panels must be 'high-density'

- $\rightarrow$  Pre-existing layouts shown on right

- → 64 isolated BNC feedthroughs per 3.5" tall panel

- 1100 RG-58 cables run from patch to five F250 VME/VXS crates in SHMS electronics hut

- $\rightarrow$  BNC on patch panel

- $\rightarrow$  LEMO in electronics hut

- Volume estimate for 1100 RG-58

- $\rightarrow$  Penetration area

- » 72 in<sup>2</sup> (min) + overhead

- $\rightarrow$  Cable tray

- » nominal 24" wide, 4-6" tall

# **HV / Slow Controls / Cabling Overview**

High Voltage

**HV Crates inside Hut**

- $\rightarrow$  High Voltage (-1.6kV @ < 1 mA base draw)

- 30x CAEN 7030N Cards » (36ch, 1mA max/ch)

- High Voltage Cables

- $\rightarrow$  2 cable runs:

- » NPS roof patch  $\rightarrow$  (~60-70 ' run)  $\rightarrow$ Patch panel rack on SHMS carriage near pivot, and

- » Patch panel rack  $\rightarrow$  (~60-70' run)  $\rightarrow$

SHMS detector hut (HV crates)

(Ignore the "Cable strain relief" concept below. It's

NPS Collab. Meeting • Feb 3, 2020

# HV / Patch Panel / Cabling Summary

### High Voltage

- → High Voltage (-1.6kV @ < 1 mA base draw)</p>

- » 30x CAEN 7030N Cards (36ch, 1mA max/ch)

- » matches 36 crystal columns

- $\rightarrow$  HV procurement complete

- » Firmware debugging w/ CAEN underway, but no show stoppers

- HV Slow Controls

- → HV monitoring and control already part of standard Hall C infrastructure, *but*

- → Will likely roll into ComCal like screens (w/ DSG support)

- High Voltage Cables (2 sets) TBP

- → Multi-conductor cabling

48 ch/cable (NPS uses 36 ch/cable)

- » NPS roof patch  $\rightarrow$

- » Patch panel rack on SHMS carriage near pivot  $\rightarrow$

- » SHMS detector hut (HV crates)

- → Work needed here!

- Signal Cables (2 sets) TBP

- $\rightarrow$  RG58 / 50 Ohm

- » NPS roof patch (LEMO)  $\rightarrow$

- » Patch panel rack on SHMS carriage near pivot (BNC)  $\rightarrow$

- » SHMS detector hut (LEMO)

- cables flow into crates from above via cable trays running above racks

- Cable run details (length) and costing in progress (Designers, A. Kenyon)

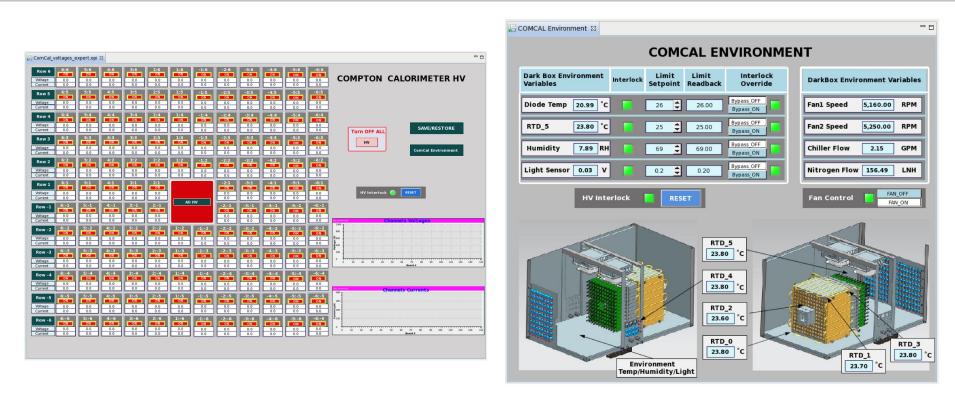

## **NPS Detector Slow Controls**

- NPS detector will need additional instrumentation for Thermal Monitoring/Control and LED system

- Thermal Monitoring/Control

- $\rightarrow$  Model after Primex/HyCal/ComCal

- $\rightarrow$  Only local control needed

- Remote monitoring is straight forward

- → Brad will be JLab point of contact for integration / EPICS

- » DSG support required for ComCal-style GUI

- Existing EPICS Archiver and Alarm Handler software used for automatic signal logging/ monitoring

- Thermal Monitoring/Control Notes

- $\rightarrow$  Rough Channel/Function List:

- » Readbacks for chiller/air-handler at minimum

- Status, in/outflow temps, etc

- $\rightarrow$  Internal air temp readback(s)

- → Multiple detector temp readbacks (few dozen ch)

- » Several locations in crystal mount

/ HV divider region

- LED controls (JLab FE Group)

- $\rightarrow$  Controller design in progress...

- » Custom control board

- » Firmware development

- → Spec documents delivered to FE group on Oct 2019

- » Chris: Hall D DIRC LED pulser design may be good starting point

# **Extend Comcal (Hall D) Screens to NPS**

- Prototype calorimeter installed in Hall D since mid-2018 is very similar to NPS.

- → Existing control screens could be extended to provide frontend user interface for NPS

- » DSG needed to take the lead on this (confirm)

# **Status/Schedule Summary**

- Support hardware proc./staging

- $\rightarrow$  Patch panel, NPS  $\rightarrow$  DAQ cabling

- » Design near complete, procurement can begin anytime (Joe, Andy, Jack, DSG)

- $\rightarrow$  HV Crates

- » Procurement complete

- Slow Controls

- → LED Control (*DSG* + *FE Group*)

- » Specs submitted to FE Group

- Confirmed w/ Chris C.

- $\rightarrow$  "Integrated" NPS controls (*DSG*)

- » ie. expand Comcal screens?

- » Confirm/schedule with DSG!

- DAQ HW Procurement (Brad) (Ongoing, complete by Fall 2020?)

- → Computer HW, Network upgrades are ongoing

- $\rightarrow$  Single board computers (5+1)

- $\rightarrow$  VTP boards (5+1)

- → VXS crate purchases ongoing (2/5 in-hand, 3 to purchase)

- → F250s available but *must*

- » Reserve when dates known!

- DAQ Firmware/SW Devel. (Should begin in 2020?)

- $\rightarrow$  3.5 person-months (FE Group)

- » Confirmed w/ Chris C.

- Analyzer (Hall C) mods

- $\rightarrow$  Should begin in 2020?

- $\rightarrow$  Who (decoding + NPS specific)?

### "To Do" Summary Slides

## "Todo List" Summary (HW)

### Remaining Procurements

$\rightarrow$  Compute HW (Brad) (ongoing) » Disk, 10 gigE, DAQ MTP trunk fiber (TBD, few \$k)  $\rightarrow$  VXS crates \$17k/ea (Brad) 3  $\rightarrow$  Modules (Brad) \$5k/ea » VME computers 5+1(Awaiting arrival) » SD boards – 4 SD boards ordered Aug '19 » VTP 5+1\$10k/ea » F250s (Phys Div) (Need to 'reserve')  $\rightarrow$  Patch Panel hardware (Joe, Jack, DSG) (\$\$\$) » HV cabling/connectors » BNC:LEMO cables – coax purchased, connectors TBP (\$\$)

# "Todo List" Summary (FW, SW)

- DAQ firmware development (FE/DAQ Group)

- $\rightarrow$ VTP firmware (clusters)

- →F250 firmware (sparsified waveform readout)

- →TI/TM firmware (to readout all NPS crates + HMS)

- →CODA ROC driver dev. (Intel 'Vivo' VME interface)

- LED control system

(FE/DAQ Group)

→HW interface board

- →Firmware control + SW

- Slow controls SW

→Comcal GUI → NPS

(DSG, confirm!)

- » HV, temp displays

- Analyzer development ("Hall C SW" + NPS)

- →Analyzer decoder

- multi-block decoding and potential related integration issues ('scaler' events, etc)

$\rightarrow$ High-level NPS class integration  $\rightarrow$  hcana

### **Backup Slides**

### **FE Group Work Commitment**

Neutral Particle Spectrometer Experiment

DAq Hardware/Firmware Development Work Commitment

2019-May-14 [Chris Cuevas]

Hardware: [B. Raydo, C. Cuevas]

- Manage procurement for five (5) new VXS crates and six (6) VXS Trigger Processor[VTP] modules

--> Includes time/resources for acceptance testing of new items

- Order and plan for installation of new MTP fiber optic trigger cable from the Hall C counting house to SHMS

- Locate and test at least fifty-one(51) Flash ADC-250 modules from the Fast Electronics/Physics 'pool'

--> Includes time/resources for testing

#### - TI/TM modifications

--> William Gu has reviewed the requirements for the NPS DAq crate configuration and has a plan to support the 5 new VXS crates for the NPS calorimeter plus the 3 HMS crates.

--> This work includes modifications to support multiple Trigger Interface "Masters"

Firmware/Simulation/Verification [B. Raydo, H. Dong, Ed J., W. Gu]

- 5 x 5 cluster based trigger development for VTPs

--> Significant development has been completed for the Heavy Photon Search experiment, so large portion of firmware can be re-used

--> Test and verify that the proper logic levels and timing latency meet the requirements to be combined with the HMS NIM trigger

--> Develop new firmware to create a sparsification list that will be sent from the VTP switch slot to the FADC250 [payload slots] The sparsification firmware is new, but the hardware path exists on VXS back-plane from the VTP to the FADC250 boards -- FADC250 firmware [H. Dong, Ed J., B. Raydo]

$\ensuremath{\text{-->}}$  The good news is that the firmware exists for modes that the NPS experiment requires

--> Features of High Resolution timing, QDC and scaler data, and raw waveform sample mode (25 samples == 100ns) exist, plus firmware to compress the readout data has been tested/used on other experiments.

--> Merging existing firmware from other experiments and functional verification/testing will be the significant activities for the FADC250 development.

#### Procurement support:

- VXS crates [Estimate  $13 \rm K/Crate]$  - Long lead item ~12weeks/After Receipt of Order

- VTP modules [Estimate \$8700/Module] Long lead item ~10weeks/ARO

- MTP Fiber Optic trunk line + Installation: \$4500 4 week delivery ARO

#### Resource commitment:

- After significant discussions with Ben Raydo, Hai Dong, Ed Jastrzembski and William Gu I estimate that 3.5 man-months will be needed to complete the activities listed. Keep in mind that this time allocation may indeed be integrated over several months, but there are significant sections of new firmware that will need to be tested well in advance of the experiment installation period. If the experiment begins in 2020-Sept, then this development work must be started as early as spring 2020.

- Long lead hardware procurement should be started as soon as funds are allocated in FY2020. This will allow for vendor fabrication time and acceptance testing.

Some details updated since May 14, 2019

Thomas Jefferson National Accelerator Facility NPS Collab. Meeting • Feb 3, 2020

### SHMS Carriage w/ Distance Annot.

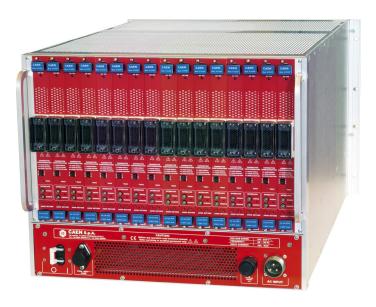

# **NPS High Voltage Supply**

- High Voltage Requirements

→ 1100 channels

→ -1.6kV @ < 1 mA base draw</li>

- Supplied by 2 CAEN SY4527 HV Chasses w/ Booster

- →16x CAEN 7030TN Cards each

- » Each card: 36ch, 1mA max/ch (matches 36 crystal columns)

- →576 ch/crate; 1152 ch total

- HV procurement complete

- $\rightarrow$ 2 Crates + 34 cards on-site

- →DSG working with CAEN on firmware issues since Fall '19

Thomas Jefferson National Accelerator Facility NPS Collab. Meeting • Feb 3, 2020

## **HV Patch Notes**

- HV patch panel will accept a 'Radiall 52' male connector

- $\rightarrow$  The connector has common ground for 48 independent channels (of which we use 36)

- $\rightarrow$  The connector ground must be isolated from the rack

- Other end will plug into CAEN 7030 cards

- $\rightarrow$  Connector map follows CAEN pinout as shown on left (from CAEN 7030 manual)

- Cables 'reversible' and reusable

- Multi-conductor cable identified

- $\rightarrow$  Teledyne Reynolds in Torrance, CA.

- » Part# 178-5790

- HV patch panel components TBP

https://www.datasheets360.com/pdf/8778225758601965736

https://www.caen.it/products/a996/

https://userweb.ilab.org/~brads/Manuals/Hardware/CAEN/A730 HV Boards-Apr2016.pdf

Thomas Jefferson National Accelerator Facility

NPS Collab. Meeting • Feb 3, 2020

**Electronic Instrumentation m**

Multipin connector pin assignment

Table 2 – 52 pin connector assignment

A/AG7030 - 7030T (CH36..47 N.

10 Cł

| .C. on / | 1/0 | 30 | & AG7030 | ))) |    |          |

|----------|-----|----|----------|-----|----|----------|

| nction   |     | #  | function |     | #  | function |

| H02      |     | 11 | RETURN   | 1   | 22 | CH01     |

| H07      |     | 12 | CH04     |     | 23 | CH06     |

| H12      |     | 13 | CH09     |     | 24 | CH11     |

| H17      |     | 14 | CH14     |     | 25 | CH16     |

| H22      |     | 15 | CH19     |     | 26 | CH21     |

| H27      |     | 16 | CH24     |     | 27 | CH26     |

| H32      |     | 17 | CH29     |     | 28 | CH31     |

| H37      |     | 18 | CH34     |     | 29 | CH36     |

| H42      |     | 19 | CH39     |     | 30 | CH41     |

| H47      |     | 20 | CH44     |     | 31 | CH46     |

|          |     | 21 | RETURN   | 1   |    |          |

|          |     |    |          |     |    |          |

| #  | function    | #  | functio |

|----|-------------|----|---------|

| 32 | RETURN      | 43 | CH00    |

| 33 | CH03        | 44 | CH05    |

| 34 | CH08        | 45 | CH10    |

| 35 | CH13        | 46 | CH15    |

| 36 | CH18        | 47 | CH20    |

| 37 | CH23        | 48 | CH25    |

| 38 | CH28        | 49 | CH30    |

| 39 | СН33        | 50 | CH35    |

| 40 | CH38        | 51 | CH40    |

| 41 | CH43        | 52 | CH45    |

| 42 | SAFETY LOOP |    |         |

### **Radiall HV Connector**

### **HIGH VOLTAGE MULTIPIN CONNECTORS**

#### DIMENSIONS :

The drawing below shows the dimensions (mm) of the plug for cable and for 52 socket contacts.

- High voltage connectors (breakdown voltage 12,5 kVdc).

- High density rectangular connectors for 23 or 52 high voltage contacts.

- Braid to braid electrical continuity achieved once plug & receptacle are mated.

- Rear release, rear removable size 23 crimp contacts.

- Interlock contacts.

These connectors have been designed for high voltage applications on four CERN experiments (ATLAS, CMS, ALICE, LHC-B) of the LHC (Large Hadron Collider) particle accelerator. For connectors with 23 or 52 contacts (size 23 crimp), there are five configurations available (see table on reverse side). The connectors can be fitted with two interlock pin contacts that switch off the power supply before unmating the standard contacts. Both interlock and standard contacts are rear release rear removable crimp contacts. The electrical continuity between the plug and the receptacle is provided by the connector pin guides.

| TECHNICAL CHARACTER                          | ISTICS :                                                                                                                                                       |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Material insulator :                         | Thermoplastic UL94V0 - halogen free - tensile strenght reduction does<br>not exceed 6% after a cumulative exposition to 5 10°Gy at a rate of<br>1 to 2 Gy / h. |

| <ul> <li>Backshell &amp; shroud :</li> </ul> | Aluminium alloy nickel plated.                                                                                                                                 |

| Locking device :                             | Stainless steel and nickel plated copper alloy.                                                                                                                |

| Contacts :                                   | Copper alloy gold over nickel plated.                                                                                                                          |

| <ul> <li>Breakdown voltage :</li> </ul>      | 12,5 kV dc.                                                                                                                                                    |

#

#### **CERN / RADIALL CROSS REFERENCES :**

| CERN P/N                                                                                                                                                                                                                                                                            | RADIALL P/N                                                                                                                                                                                                            | Designation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09.41.34.700.2<br>09.41.34.720.8<br>09.41.34.720.8<br>09.41.34.705.7<br>09.41.34.730.6<br>09.41.34.500.8<br>09.41.34.500.8<br>09.41.34.505.3<br>09.41.34.510.6<br>09.41.34.510.6<br>09.41.33.840.5<br>09.41.33.820.9<br>09.41.33.820.9<br>09.41.33.830.7<br>09.41.33.880.7<br>T.B.D | 691802002<br>691802004<br>691803002<br>691803006<br>691803006<br>691802003<br>691802005<br>691803003<br>691803005<br>691803007<br>691804200<br>691804200<br>691804201<br>691804301<br>691804331<br>691804231<br>282281 | Plug for cable and for 52 socket contacts<br>Plug for cable and for 52 pin contacts<br>Receptacle for cable and for 52 pin contacts<br>Receptacle for front panel and for 52 pin contacts<br>Receptacle for front panel and for 52 pin contacts<br>Plug for cable and for 23 pin contacts<br>Receptacle for front panel and for 23 socket contacts<br>Size 23 pin contact for 0,12mm <sup>2</sup> cross section cable<br>Size 23 socket contact for 0,12mm <sup>2</sup> cross section cable<br>Size 23 socket contact for 0,12mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,12mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,02mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,02mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,02mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,02mm <sup>2</sup> cross section cable<br>Size 23 interlock pin contact for 0,02mm <sup>2</sup> cross section cable |

| T.B.D<br>T.B.D                                                                                                                                                                                                                                                                      | 282585001<br>282549024                                                                                                                                                                                                 | Positioner<br>Insertion / extraction tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

For further information please contact your nearest Radiall representative

#### ISO 9001 APPROVED

https://www.datasheets360.com/pdf/8778225758601965736 https://www.caen.it/products/a996/

RADIALL do Brasil (Brasil)

+55 21 25 58 05 76

SHANGHAI RADIALL Ltd (China)

+86 21 66 52 37 80

NIHON RADIALK (Japan)

+861 3 386 22390

RADIALL Electronics Ltd (Asia)

+852 29 59 38 33

RADIALL Electronics (Ltd (Asia))

+91 80 83 95 271

+1 480 730 5700

### **Multiconductor HV Cable**

- Multiconductor cable recommendation

- $\rightarrow$  Teledyne Reynolds

- Part# 178-5790

- » Ph: (310) 823.5491

- » Em: tr\_sales@teledyne.com

- $\rightarrow$  Used by CERN, CAEN

| FEP      |     |            |

|----------|-----|------------|

| FEATURES | AND | PROPERTIES |

Heritage Quality Performance

Extruded, FEP insulated, high voltage wire and cable offers exceptional dielectric strength without the disadvantages common to equally rated silicone rubber insulated cables. As a result, cable assemblies or cable bundles are smaller in diameter, volume and in bend radius thus allowing the system designer to better utilize space within their system. Also, its molecular structure gives it excellent durability and resistance to dielectrid/cooling fluid degradation.

FEP insulation, being a harder material than silicone rubber, is not prone to "pin-holing" and high voltage "punch-thru" when the cable surface is abraded or when strands break during in-field servicing. FEP is also more resistant to damage when making contact with sharp edges. Even so, sharp edges should always be avoided.

Although FEP is generally difficult to bond to, Teledyne Reynolds, has developed a Ready-to-Bond<sup>™</sup> product line that is manufactured using proprietary abrading and surface preparation techniques that enable excellent silastic bonds. Teflon® tape wrapped cable, which is similar to FEP in dielectric strength and corona inception, is difficult to bond to because of its multiple spiral cross section, irregular surface and variations in diameter. Therefore, FEP cable should not only be considered for use in cable assemblies, but as high voltage hook-up wire within encapsulated high voltage power supplies, TMTs and transformers.

#### PROPERTIES OF FEP FLUOROCARBON RESIN

| Physical, Thermal and Electrical Properties | Typical Values        |

|---------------------------------------------|-----------------------|

| Specific Gravity                            | 2.14                  |

| Tensile Strength (PSI)                      | 3500                  |

| Elongation (%)                              | .325                  |

| Flexual Modules (PSI)                       | 90,000                |

| Thermal Conductivity (cal/sec-cm °F)        | 6x10 <sup>-4</sup>    |

| Thermal Expansion (in/in/ °F)               | 7.5 x 10 <sup>5</sup> |

| Continuous Use Temperature (°C)             | 204                   |

| Melt Temperature (°C)                       | 255-265               |

| Low Temperature Limit (°C)                  | -240                  |

| Hardness Durometer                          | D56                   |

| Water Absorption (%)                        | <01                   |

| Flame Resistance                            | Excellent             |

| Dieletric Constant, 60-106 Hz               | 2.1                   |

| Dissipation Factor, 60-106 Hz               | <.0007                |

| Volume Resistivity (Ohms-cm)                | <1018                 |

| Surface Resistivity (Ohm/square)            | <1016                 |

| Resistance to:                              | Rating                |

| Cold Flow or Cut Through                    | Fair                  |

| Ultraviolet Radiation                       | Excellent             |

| Electro-Mechanical Stress Cracking          | Excellent             |

| Chemical-Mechanical Stress Cracking         | Excellent             |

Conductor Material: Copper

Conductor Finish: Silver plated per test requirements of ASTM B298. Meets solderability per MIL-STD-202.

Note: Pre-conditioning of FEP cable after cutting to length is recommended because FEP cable will shrink when exposed to temperature cycling. Preconditioning should be conducted in an air circulating oven at 204°C (400°F) for one hour. No attempt should be made to condition wire or cable in bulk form or while spooled.

Teflon<sup>®</sup> is a registered trademark of Dupon

Approved for Public Release: MP/022/15

Thomas Jefferson National Accelerator Facility NPS Collab. Meeting • Feb 3, 2020

Rev. 092515

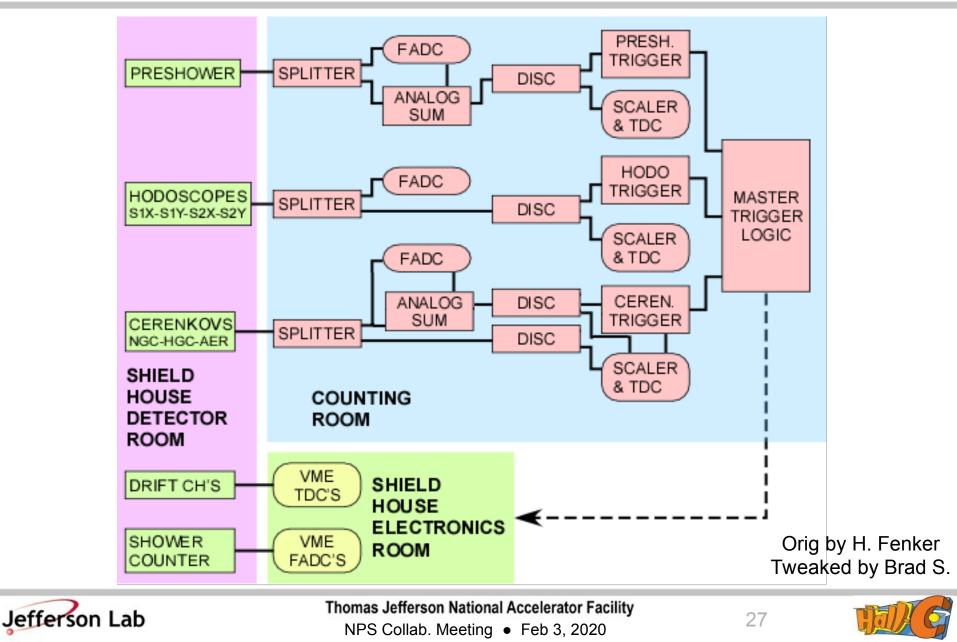

### Existing SHMS + HMS Standard DAQ Triggers and Hardware

## **SHMS/HMS Trigger/Electronics**

### **SHMS Instrumentation**

### • SHMS

### $\rightarrow$ ROC2: CH

- » Hodoscopes, Cerenk.

- FADC + 1190s

- » Misc. Signals

- ie. Triggers, Hel

- $\rightarrow$  ROC4: SHMS hut

- » Shower + Preshower

- FADCs

- $\rightarrow$  ROC6: SHMS hut

- » Drift chambers

- 1190 TDCs

- $\rightarrow$  ROC8: CH

- » Hardware scalers

- » BCMs, Helicity gated scalers

### **HMS Instrumentation**

### • HMS

### $\rightarrow$ ROC1: CH

- » Calor, Hodoscopes, Cerenk.

- FADC + 1190s

- » Misc. Signals

- ie. Triggers, Hel

### $\rightarrow$ ROC3: HMS hut

» Drift chambers

– 1190 TDCs

### $\rightarrow$ ROC5: CH

- » Hardware scalers

- » BCMs, Helicity gated scalers

## JLab F250 FADCs

- JLab FADCs

- → Constantly digitizing input voltage every 4ns

- → Multi-hit 'ADC'!

- » Can readout anything within an ~8 usec ring buffer

- $\rightarrow$  Each 'Hit' contains

- » Integrated charge

- » Peak Amplitude

- » Timing (~ 1 ns)

- » Pedestal meas.

- » Pulse profile / 'Scope trace' (\*)

- $\rightarrow$  Scaler data too

- → Pipeline capable, deep buffer, etc..

- Differences from older QDCs

→ Multi-hit!

- Must identify the 'good' hit using, for example, a timing cut

### CAEN 1190 TDCs

- CAEN 1190

- $\rightarrow$  Multi-hit TDC

- $\rightarrow$  128 channels/module

- $\rightarrow$  ~100 ps resolution

- → Pipeline capable, deep buffer, etc...

- Differences from older TDCs:

- →Module's "Common Stop" is not a good timing reference!

- » Primary function is to initiate a "Read" in the module.

- →Requires a "reference time" to measured in one of the 128 inputs

## **Available SHMS / HMS <u>Pre-Triggers</u>**

- Scintillator Planes: S1x, S1y, S2x, S2y

- SCIN = 3/4 { S1x, S1y, S2x, S2y }

- CER = Cerenkov Sum

- STOF = [S1x.OR.S1y] .and. [S2x .OR. S2y]

- PSh\_Hi = Preshower sum, 'high-threshold'

- PSh\_Lo = Preshower sum, 'low-threshold'

- EL-Hi = SCIN .and. PSh\_Hi

- EL-Lo = 2/3{SCIN, STOF, PSh\_Lo} .and. CER

- EL-Real = EL-Hi .or. EL-Lo

- EL-Clean = EL-Hi .and. EL-Lo

- Pulser/Random trigger

- $\rightarrow$  EDTM injection for deadtime monitoring, trigger setup, etc

- $\rightarrow$  EDTM should always be ON and set to nominal 10 Hz

- Each arm has its own Trigger Master (behaves like a TS)

- $\rightarrow$  Maximum of 6 trigger inputs on Trigger Master modules

- $\rightarrow$  Both coincidence and independent/parallel-arm operation available

- We use TM module for trigger prescaling

- NOTE: There is *no* Calorimeter Sum for SHMS trigger

- $\rightarrow$  SHMS Pre-Shower sum *does* exist

Thomas Jefferson National Accelerator Facility NPS Collab. Meeting • Feb 3, 2020

# **Coincidence Mode Triggers**

- SHMS Trigger Master controls all SHMS + HMS crates in 'Coin. Mode'

- → Still a single TM, so still maximum of 6 triggers for SHMS\_singles + HMS\_singles + and Coin. triggers

- $\rightarrow$  For example, these are the current triggers:

- » T1: SHMS 3/4

- » T2: SHMS EL\_real

- » T3: HMS EL\_real

- » T4: HMS 3/4

- » T5: (COIN) SHMS 3/4 .AND. HMS EL\_real

- » T6: (COIN) SHMS 3/4 .AND. HMS 3/4