# Introduction to FADC based detector class

Hanjie Liu

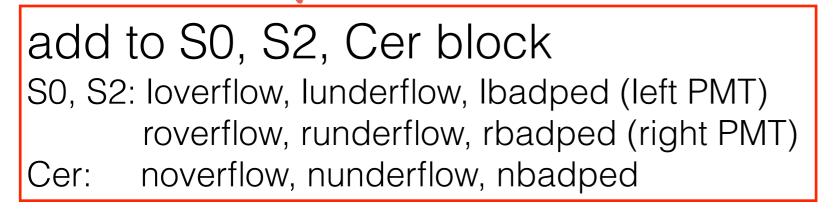

- new things added to FADC based detector class: S0, S2, Cer;

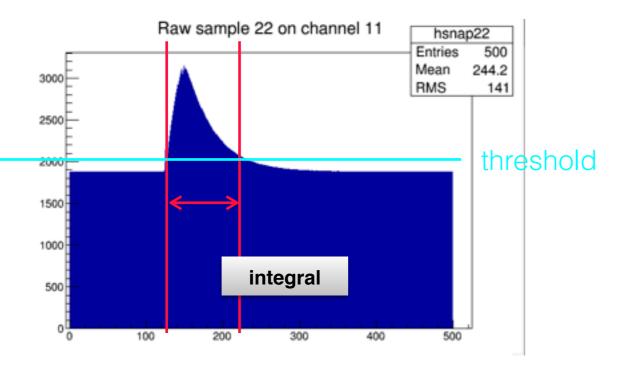

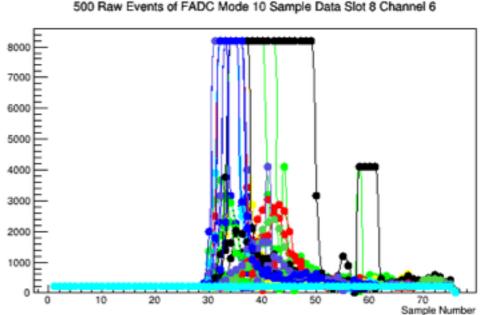

- useful FADC data when threshold is set;

- current FADC configuration for both arms;

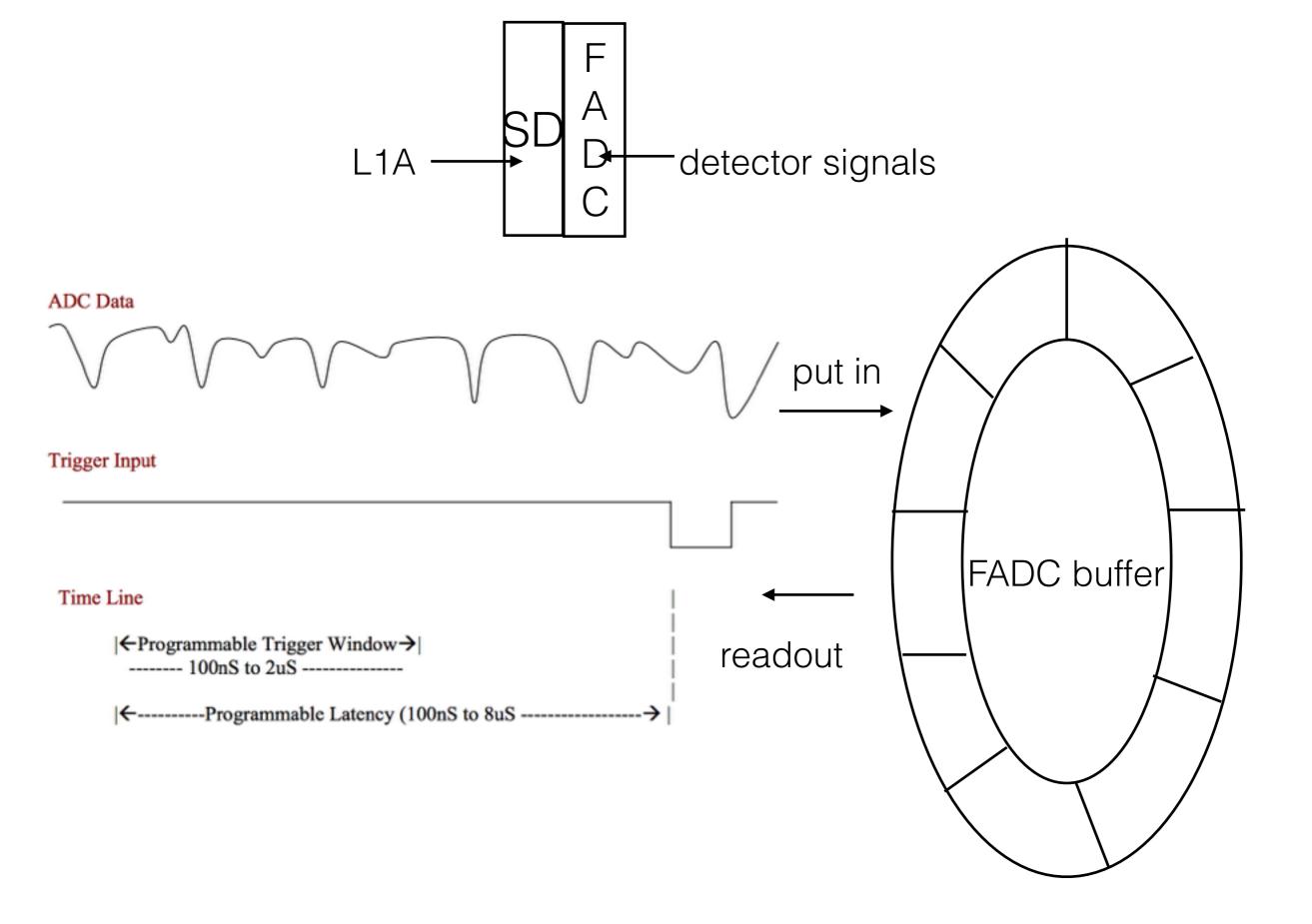

# Pulse integral mode (mode 9)

Integral number

For each event:

- integral number

- time crossing the threshold

- pedestal

For each event:

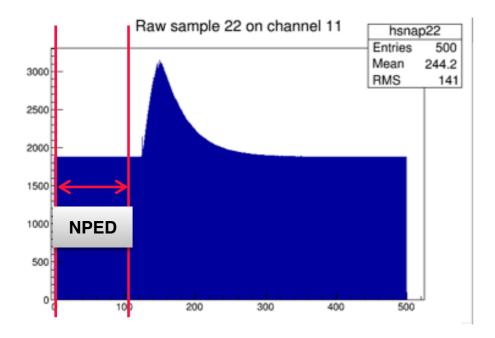

- sum first NPED samples as pedestal sum

- ped = ped\_sum/NPED \* Integral\_window

- in S0, S2, Cer database: NPED, Win

needs to be same as what are in FADC readout list

## Parameters for pulse quality

• overflow bit:

when one or more samples of a pulse is overflow, the overflow bit will be set to 1, and the value of overflow samples will be 4095 (maximum pulse value)

• underflow bit:

when one or more samples of a pulse is underflow, the underflow bit will be set to 1, and the value of underflow samples will be 0;

• pedestal quality bit:

when any of NPED samples is greater than MAXPED or is underflow or overflow, this bit will be set to 1. In this case, FADC based detector class will use the average pedestal in DB as the pedestal for this event.

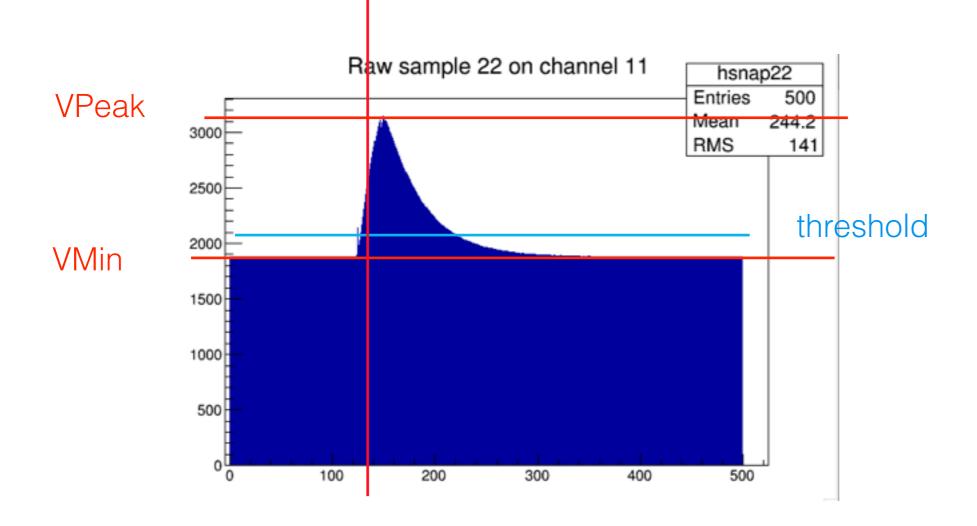

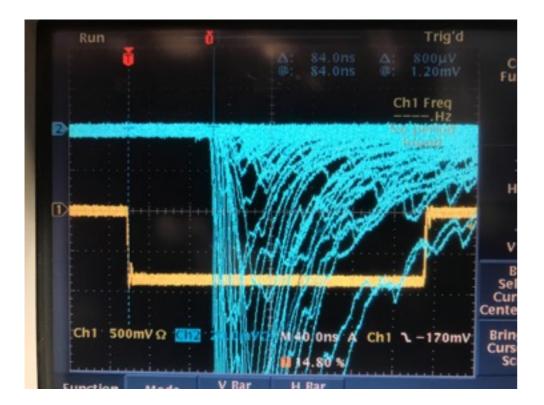

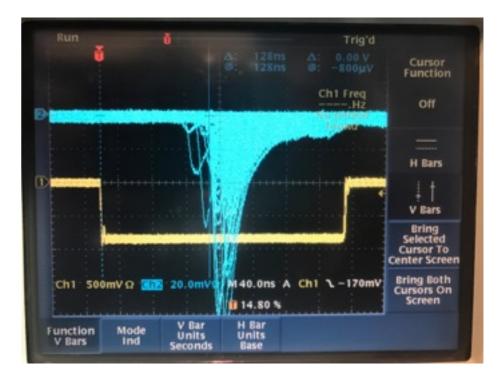

## Parameters might help when use threshold

When having threshold, will have:

- VPeak: value of pulse peak;

- number of samples within integral window that it's above threshold;

- TF: fine time of half pulse;

-----

no time walk effect

TF= time of (VPeak+VMin)/2 in the unit of 62.5ps

# FADC configuration settings

# LHRS

|                      | Slot 6<br>(s2_la) | Slot 7<br>(s2_ra) | Slot 8<br>(s0 & cer) | Slot 9<br>(Raster &<br>BPM) |

|----------------------|-------------------|-------------------|----------------------|-----------------------------|

| PL                   | 71                | 71                | 71                   | 71                          |

| PTW                  | 50                | 50                | 50                   | 50                          |

| NSB                  | 3                 | 3                 | 3                    | 3                           |

| NSA                  | 50                | 50                | 50                   | 50                          |

| NPED                 | 15                | 15                | 15                   | 15                          |

| MAXPED               | 160               | 160               | 160                  | 160                         |

| DAC                  | 3200              | 3200              | 3220                 | 2500                        |

| voltage<br>range (V) | 0.5               | 0.5               | 0.5                  | 2                           |

### RHRS

|                      | Slot 13<br>(s2_la) | Slot 14<br>(s2_ra) | Slot 15<br>(s0 & cer) | Slot 16<br>(Raster &<br>BPM) |

|----------------------|--------------------|--------------------|-----------------------|------------------------------|

| PL                   | 65                 | 65                 | 65                    | 65                           |

| PTW                  | 55                 | 55                 | 55                    | 55                           |

| NSB                  | 2                  | 2                  | 2                     | 2                            |

| NSA                  | 55                 | 55                 | 55                    | 55                           |

| NPED                 | 15                 | 15                 | 15                    | 15                           |

| MAXPED               | 160                | 160                | 160                   | 160                          |

| DAC                  | 3200               | 3200               | 3220                  | 2500                         |

| voltage<br>range (V) | 0.5                | 0.5                | 0.5                   | 2                            |

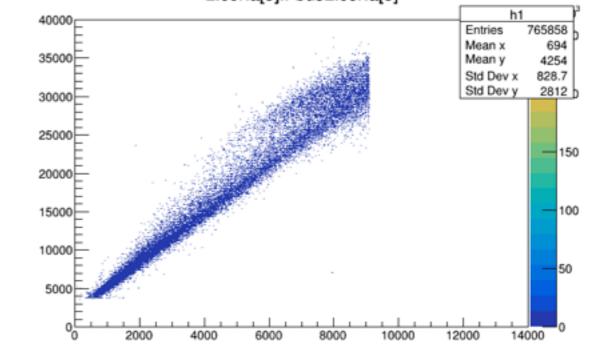

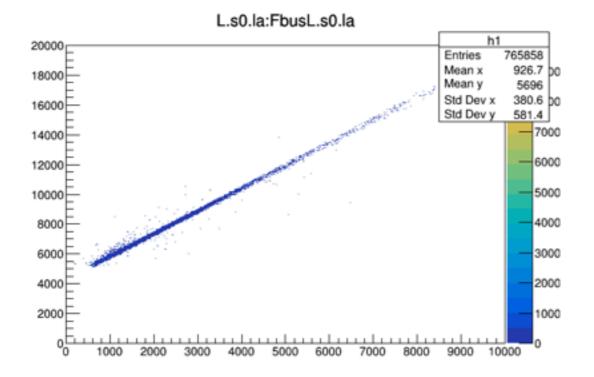

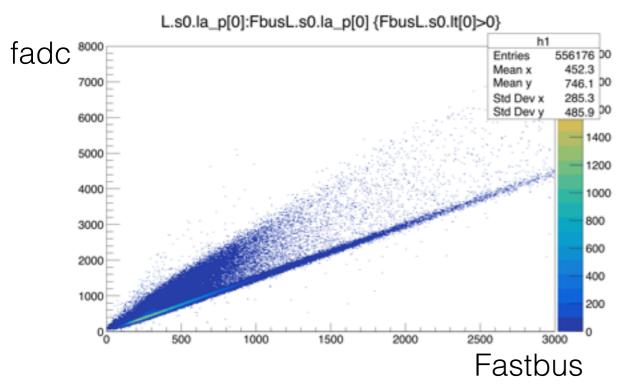

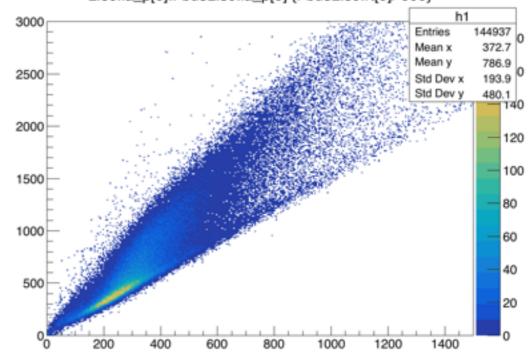

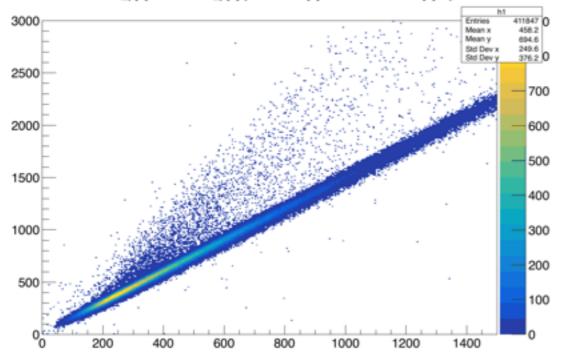

### plots from Tong Su

L.s0.la\_p[0]:FbusL.s0.la\_p[0] {FbusL.s0.rt[0]>600}

L.s0.la\_p[0]:FbusL.s0.la\_p[0] {FbusL.s0.rt[0]<600&&FbusL.s0.rt[0]>0}

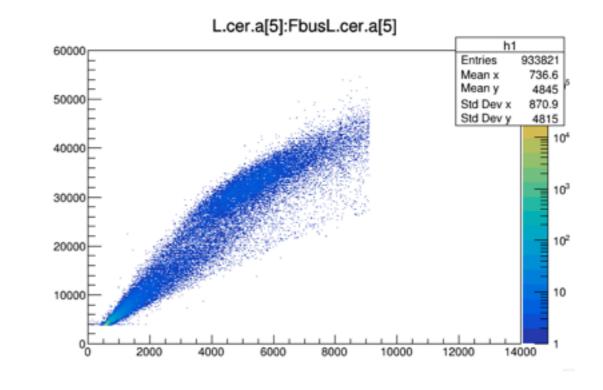

L.cer.a[5]:FbusL.cer.a[5]